Functional Description

2-2 Copyright © 2009 ARM Limited. All rights reserved. ARM DDI 0432C

Non-Confidential ID112415

2.1 About the functions

The Cortex-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an

AMBA AHB-Lite interface and includes an NVIC component. It also has optional

hardware debug functionality. The processor can execute Thumb code and is

compatible with other Cortex-M profile processors.

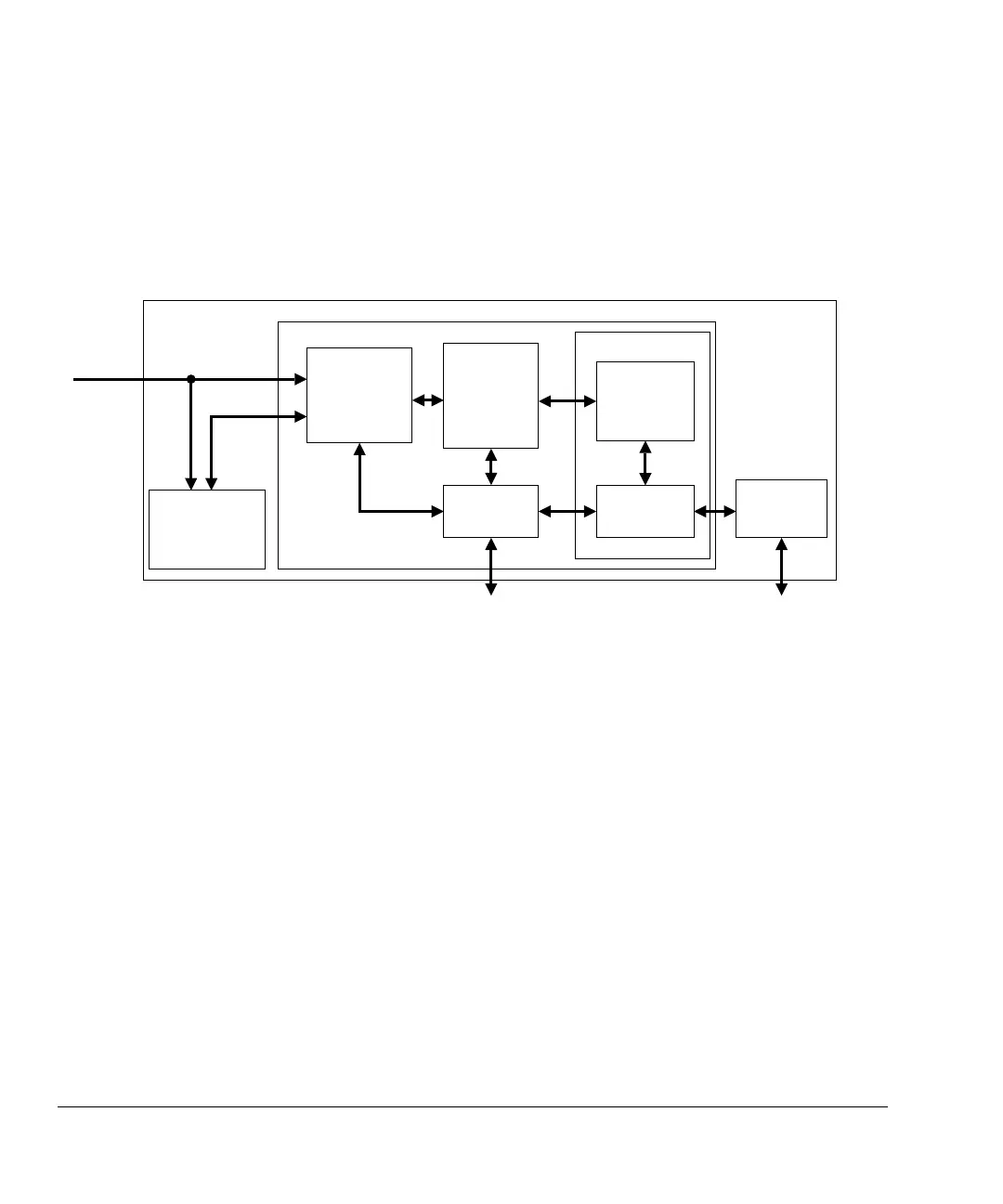

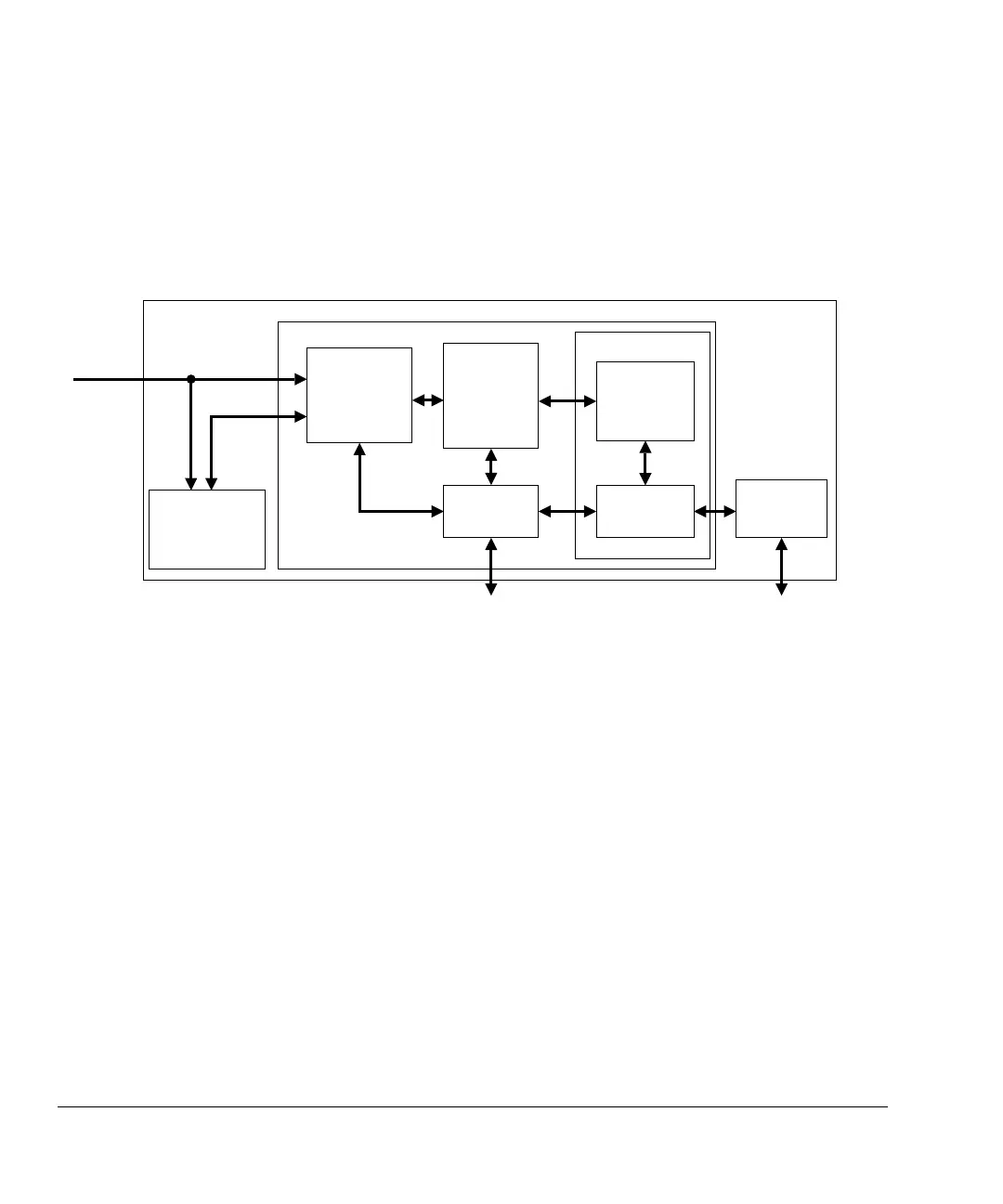

Figure 2-1 shows the functional blocks of the processor.

Figure 2-1 Functional block diagram

The implemented device provides:

• A low gate count processor that features:

— The ARMv6-M Thumb

®

instruction set.

— Thumb-2 technology

— Optionally, an ARMv6-M compliant 24-bit SysTick timer.

— A 32-bit hardware multiplier. This can be the standard single-cycle

multiplier, or a 32-cycle multiplier that has a lower area and performance

implementation.

— The system interface supports either little-endian or byte invariant

big-endian data accesses.

— The ability to have deterministic, fixed-latency, interrupt handling.

— Load/store-multiples and multicycle-multiplies that can be abandoned and

restarted to facilitate rapid interrupt handling.

— C Application Binary Interface compliant exception model.

Cortex-M0 processor

Cortex-M0

processor

core

Bus matrix

Nested

Vectored

Interrupt

Controller

(NVIC)

Interrupts

‡Wakeup

Interrupt

Controller (WIC)

‡Debug

Access Port

(DAP)

AHB-Lite interface ‡Serial Wire or JTAG debug port

‡ Optional component

Debug

‡Debugger

interface

‡Breakpoint

and

watchpoint

unit

Cortex-M0 components

Loading...

Loading...