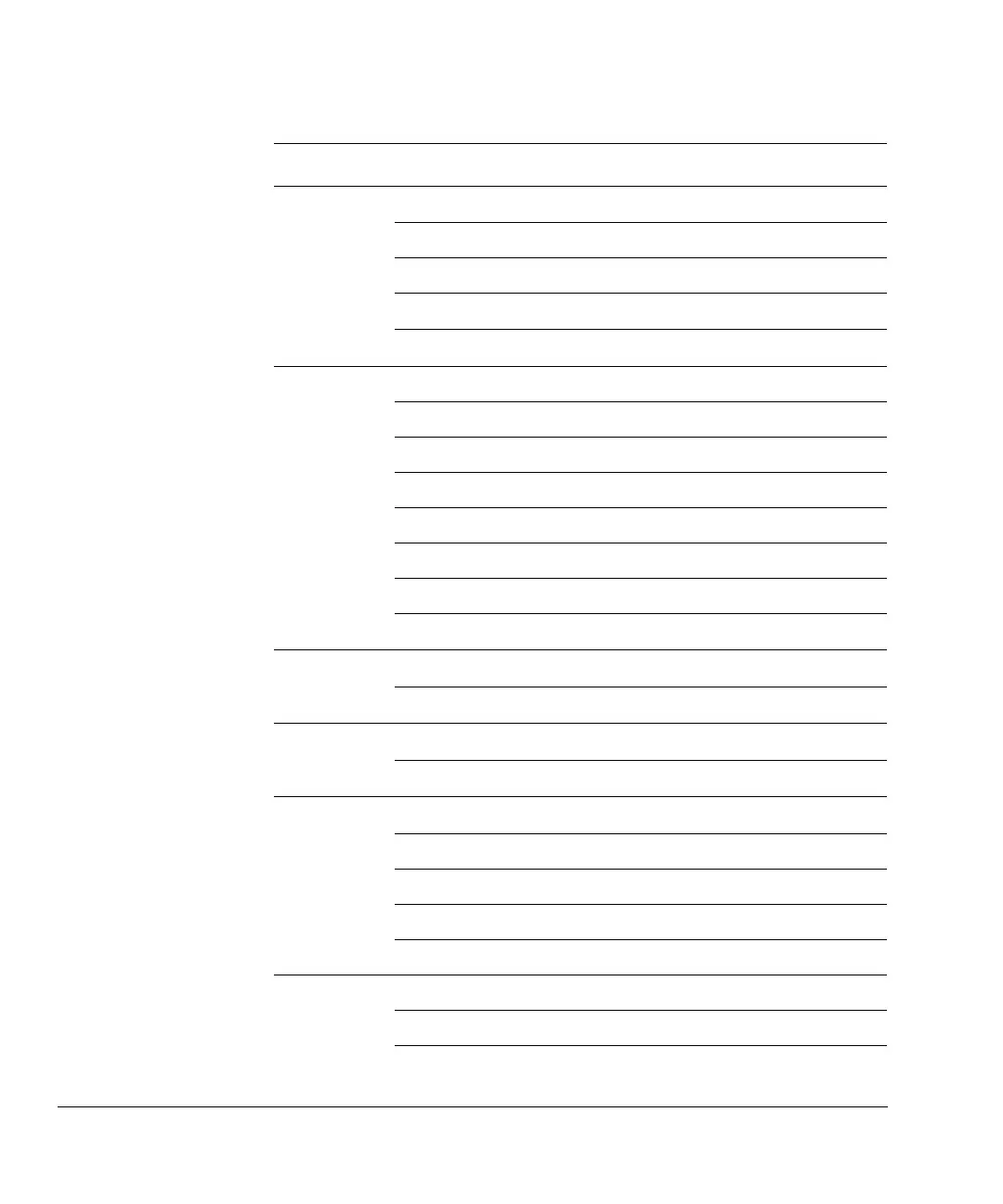

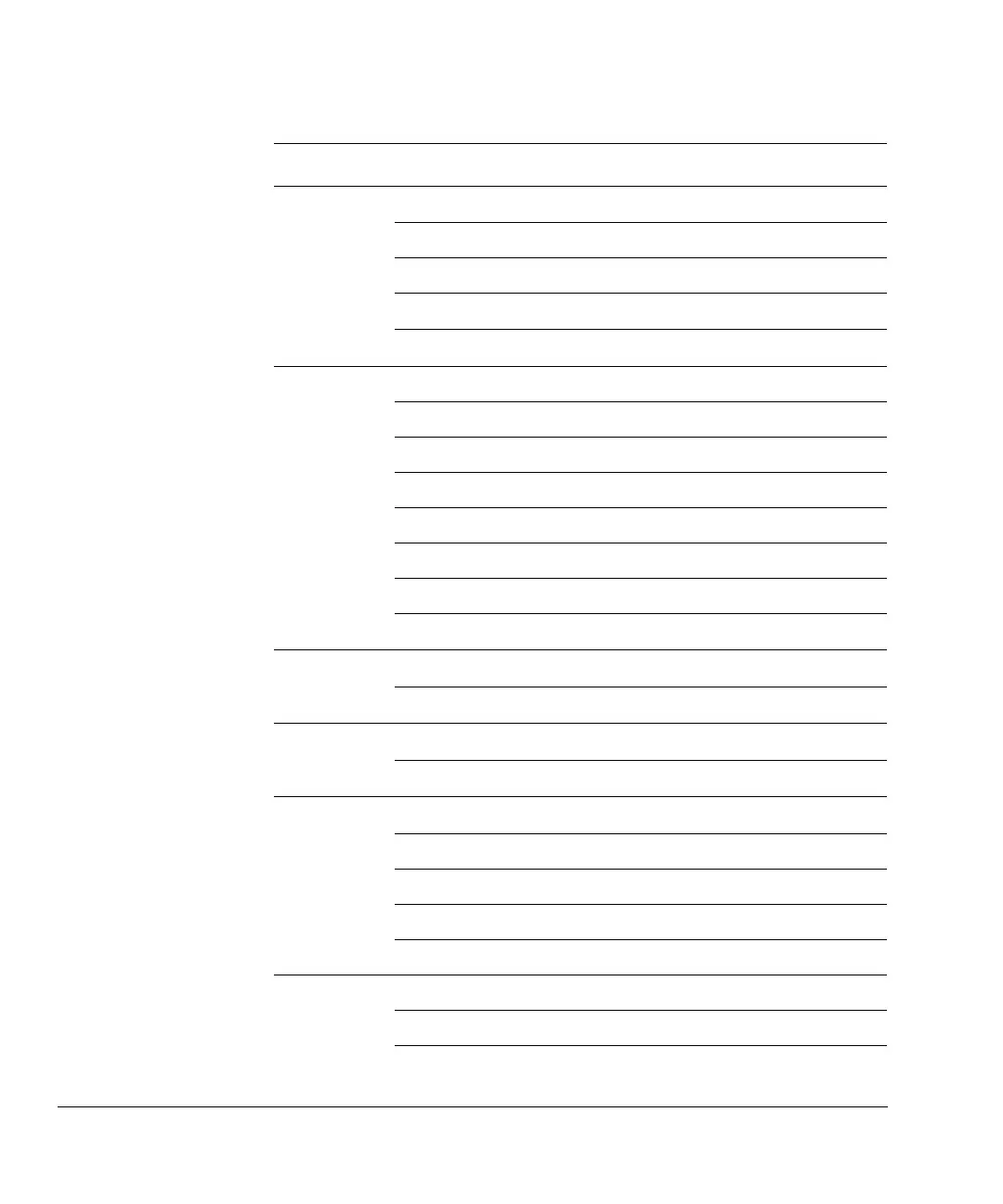

Programmers Model

3-6 Copyright © 2009 ARM Limited. All rights reserved. ARM DDI 0432C

Non-Confidential ID112415

Load Signed byte, register offset

LDRSB

Rd

, [

Rn

,

Rm

]2

PC-relative

LDR

Rd

,

<label>

2

SP-relative

LDR

Rd

, [

SP

,

#<imm>

]2

Multiple, excluding base

LDM

Rn

!, {

<loreglist>

}

1+N

b

Multiple, including base

LDM

Rn

, {

<loreglist>

}

1+N

b

Store Word, immediate offset

STR

Rd

, [

Rn

,

#<imm>

]2

Halfword, immediate offset

STRH

Rd

, [

Rn

,

#<imm>

]2

Byte, immediate offset

STRB

Rd

, [

Rn

,

#<imm>

]2

Word, register offset

STR

Rd

, [

Rn

,

Rm

]2

Halfword, register offset

STRH

Rd

, [

Rn

,

Rm

]2

Byte, register offset

STRB

Rd

, [

Rn

,

Rm

]2

SP-relative

STR

Rd

, [

SP

,

#<imm>

]2

Multiple

STM

Rn

!, {<

loreglist

>}

1+N

b

Push Push

PUSH

{<

loreglist

>}

1+N

b

Push with link register

PUSH

{

<loreglist>

,

LR

}

1+N

b

Pop Pop

POP

{

<loreglist>

}

1+N

b

Pop and return

POP

{

<loreglist>

,

PC

}

4+N

c

Branch Conditional

B<cc> <label>

1 or 3

d

Unconditional

B

<label>

3

With link

BL

<label>

4

With exchange

BX

Rm

3

With link and exchange

BLX

Rm

3

Extend Signed halfword to word

SXTH

Rd

,

Rm

1

Signed byte to word

SXTB

Rd

,

Rm

1

Unsigned halfword

UXTH

Rd

,

Rm

1

Table 3-1 Cortex-M0 instruction summary (continued)

Operation Description Assembler Cycles

Loading...

Loading...