Debug

6-4 Copyright © 2009 ARM Limited. All rights reserved. ARM DDI 0432C

Non-Confidential ID112415

6.1.1 Cortex-M0 ROM table identification and entries

Table 6-1 shows the ROM table identification registers and values for debugger

detection. This permits debuggers to identify the processor and its debug capabilities.

The Cortex-M0 ROM table only supports word size transactions.

Table 6-2 shows the CoreSight components that the Cortex-M0 ROM table points to.

The values depend on the implemented debug configuration.

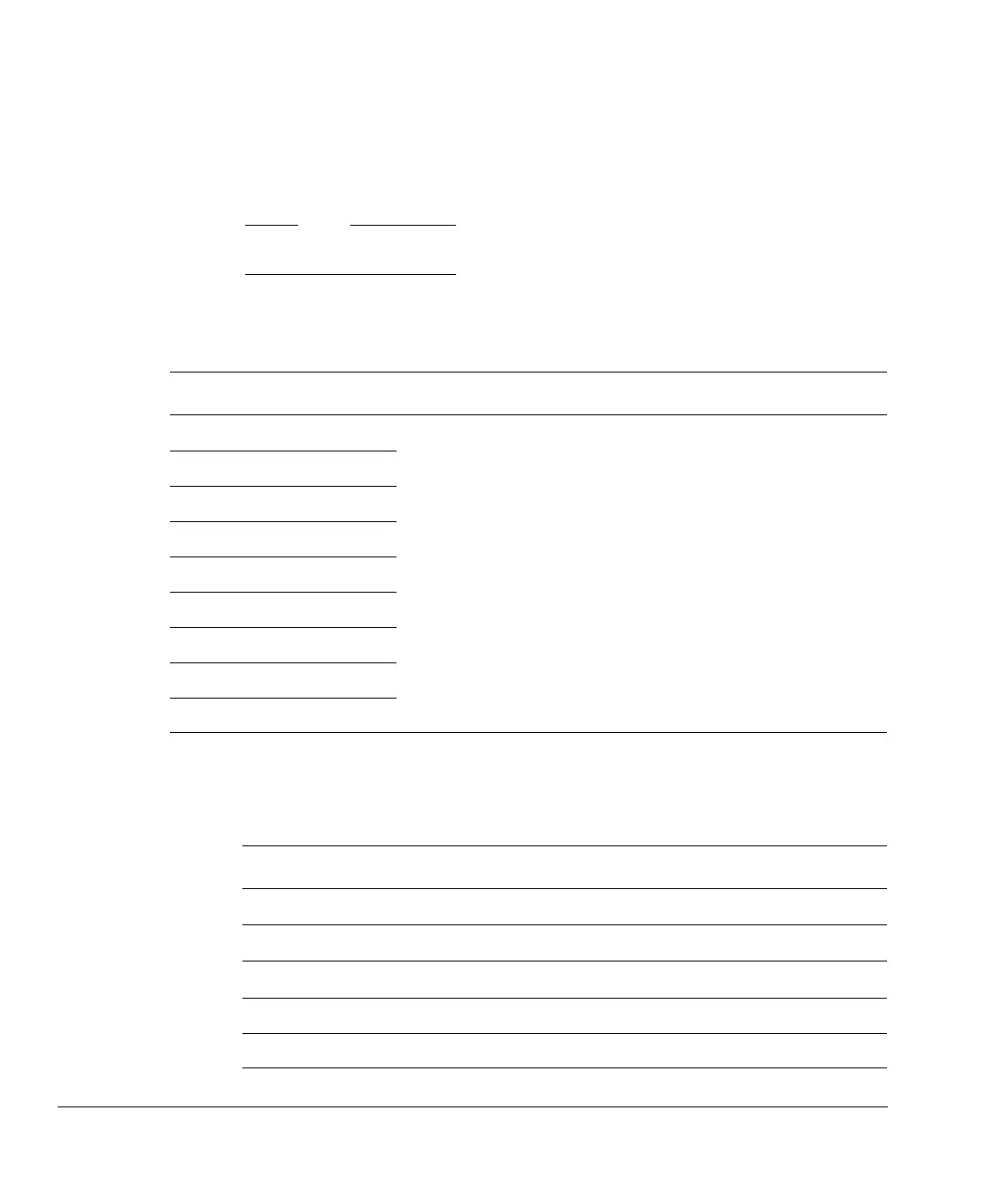

Table 6-1 Cortex-M0 ROM table identification values

Register Value Description

Peripheral ID4

0x00000004

Component and peripheral ID register formats in the ARMv6-M ARM

Peripheral ID0

0x00000071

Peripheral ID1

0x000000B4

Peripheral ID2

0x0000000B

Peripheral ID3

0x00000000

Component ID0

0x0000000D

Component ID1

0x00000010

Component ID2

0x00000005

Component ID3

0x000000B1

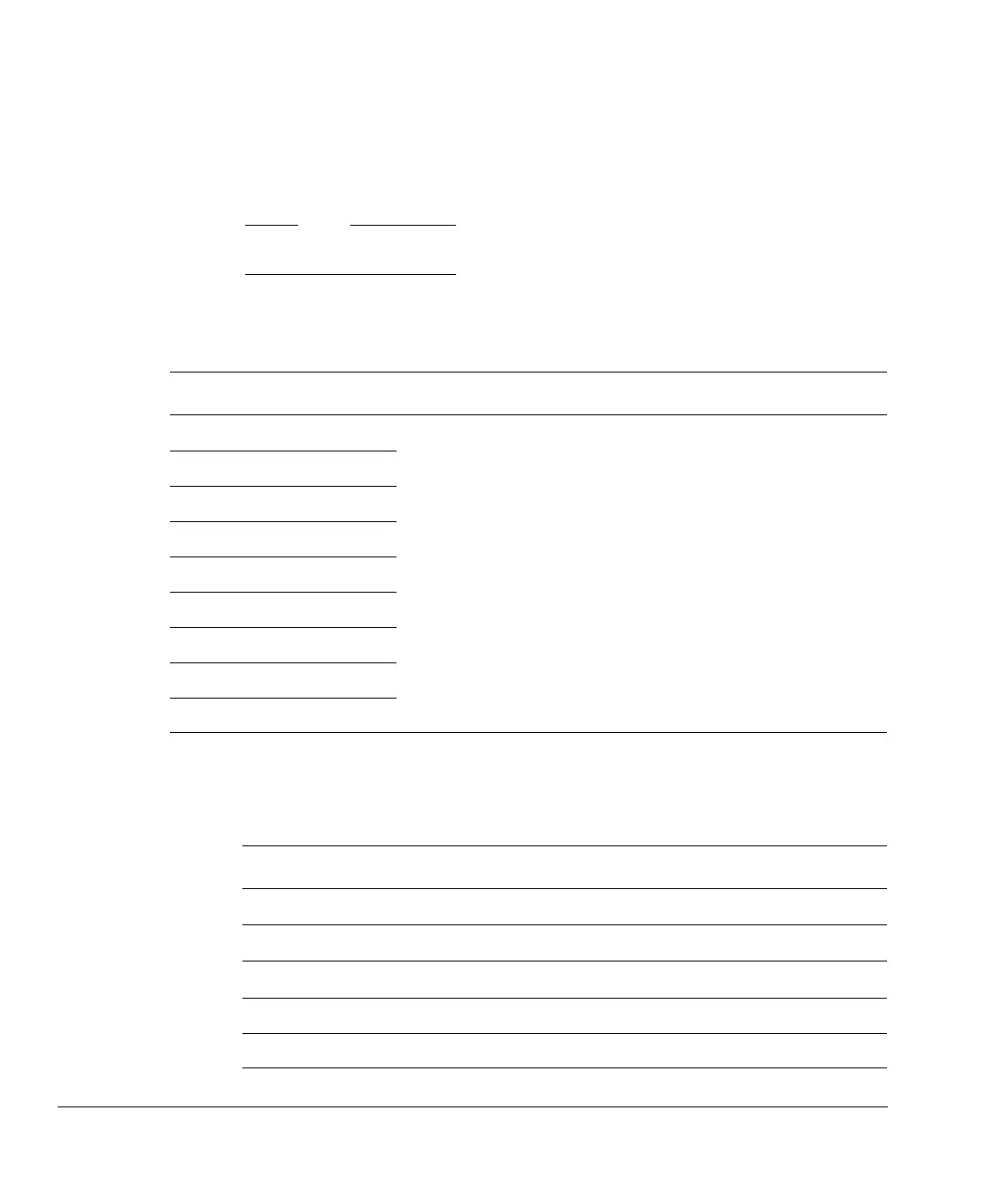

Table 6-2 Cortex-M0 ROM table components

Component Value Description

SCS

0xFFF0F003

See System Control Space on page 6-5

DWT

0xFFF02003

a

See Data watchpoint unit on page 6-6

BPU

0xFFF03003

b

See Breakpoint unit on page 6-7

End marker

0x00000000

See DAP accessible ROM table in the ARMv6-M ARM

MemType

0x00000001

See CoreSight management registers in the ARMv6-M ARM

Loading...

Loading...