Introduction

ARM DDI 0432C Copyright © 2009 ARM Limited. All rights reserved. 1-5

ID112415 Non-Confidential

1.4 Configurable options

Table 1-1 shows the processor configurable options available at implementation time.

1.4.1 Configurable multiplier

The

MULS

instruction provides a 32-bit x 32-bit multiply that yields the least-significant

32-bits. The processor can implement

MULS

in one of two ways:

• as a fast single-cycle array

• as a 32-cycle iterative multiplier.

The iterative multiplier has no impact on interrupt response time because the processor

abandons multiply operations to take any pending interrupt.

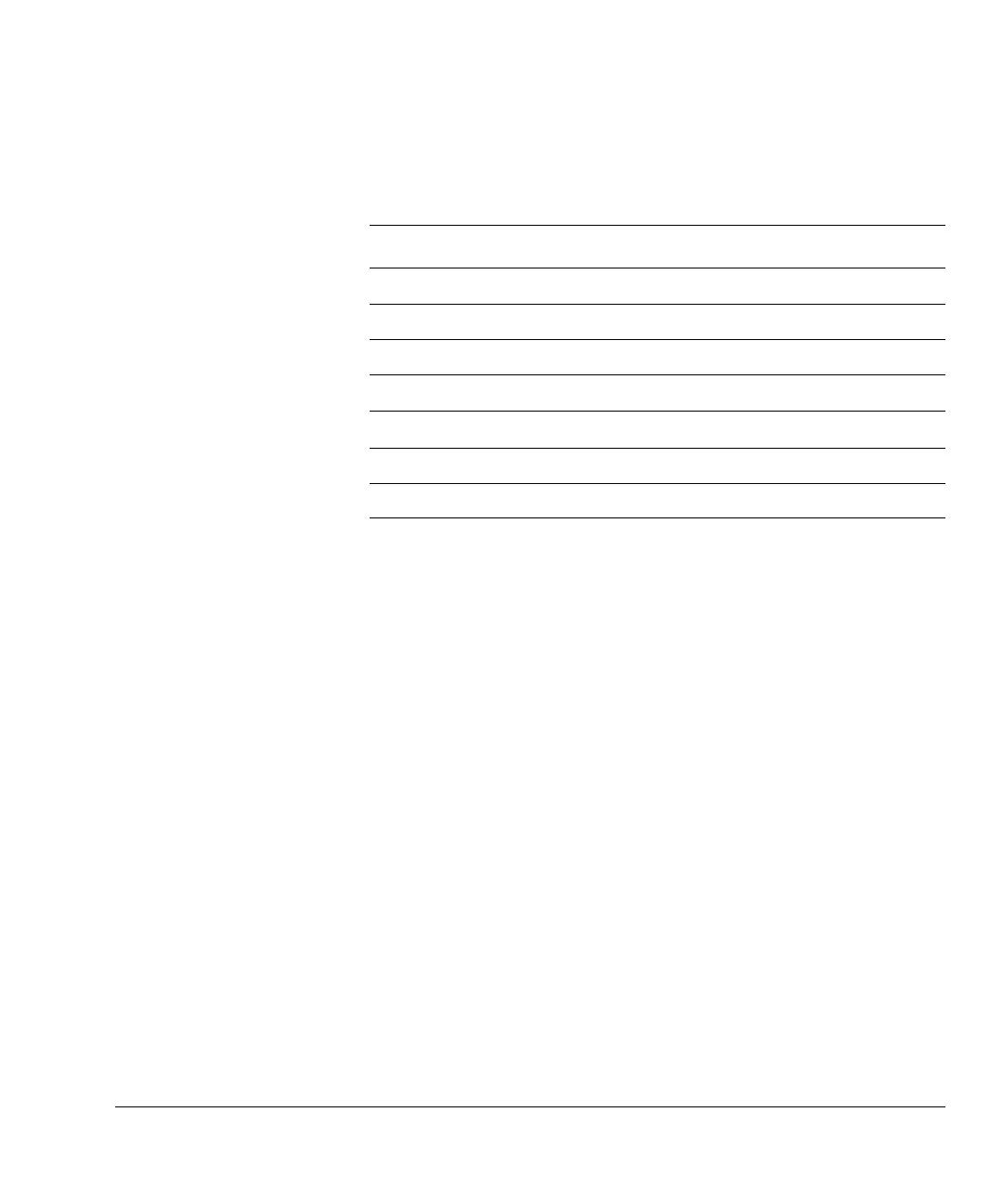

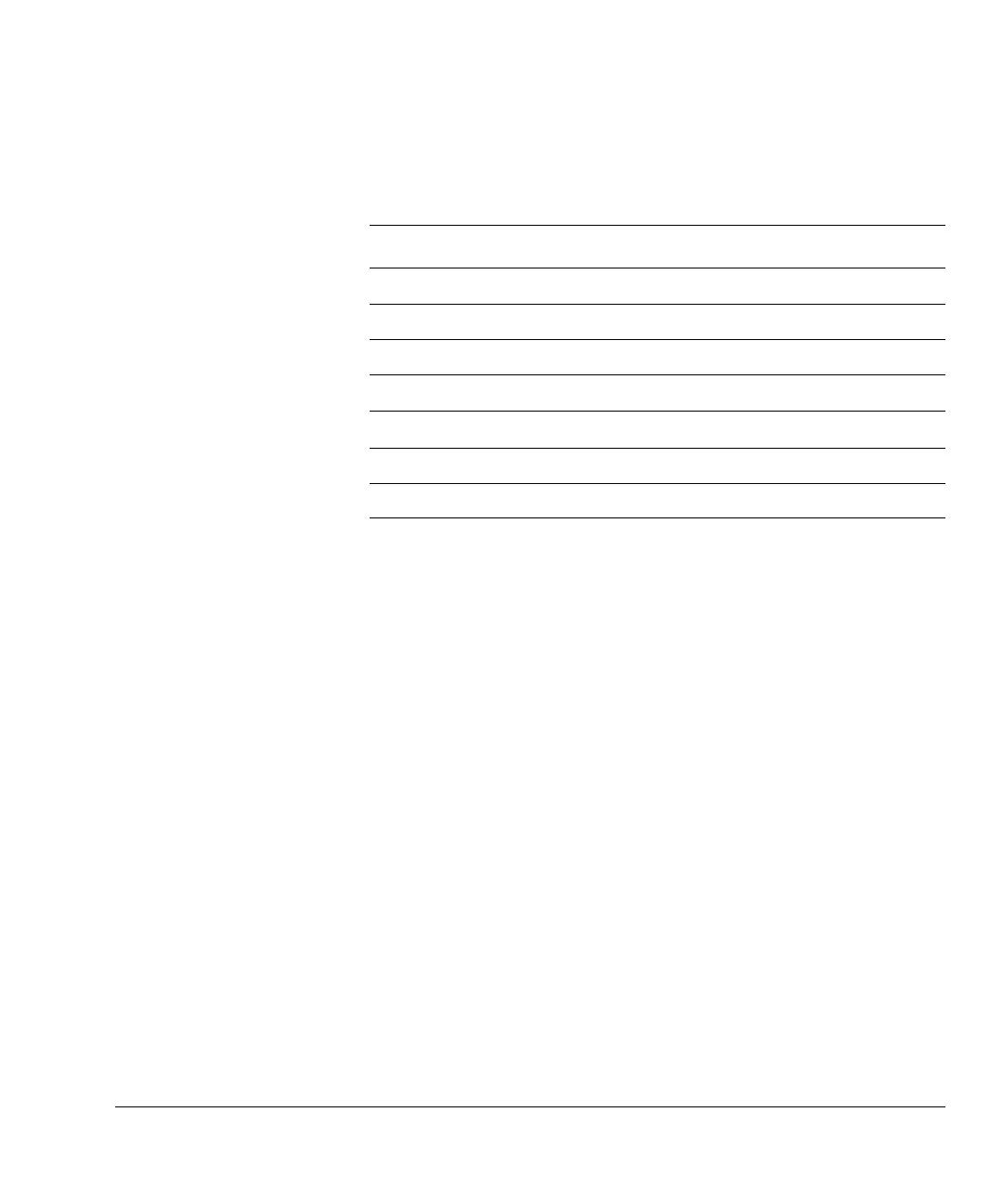

Table 1-1 Processor configurable options

Feature Configurable option

Interrupts External interrupts 1, 2, 4, 8, 16, 24 or 32

Data endianness Little-endian or big-endian

SysTick timer Present or absent

Number of watchpoint comparators

a

a. Only when halting debug support is present.

0, 1, 2

Number of breakpoint comparators

a

0, 1, 2, 3, 4

Halting debug support Present or absent

Multiplier Fast or small

Loading...

Loading...