UD70

Issue code: 70nu2

8-34 Features

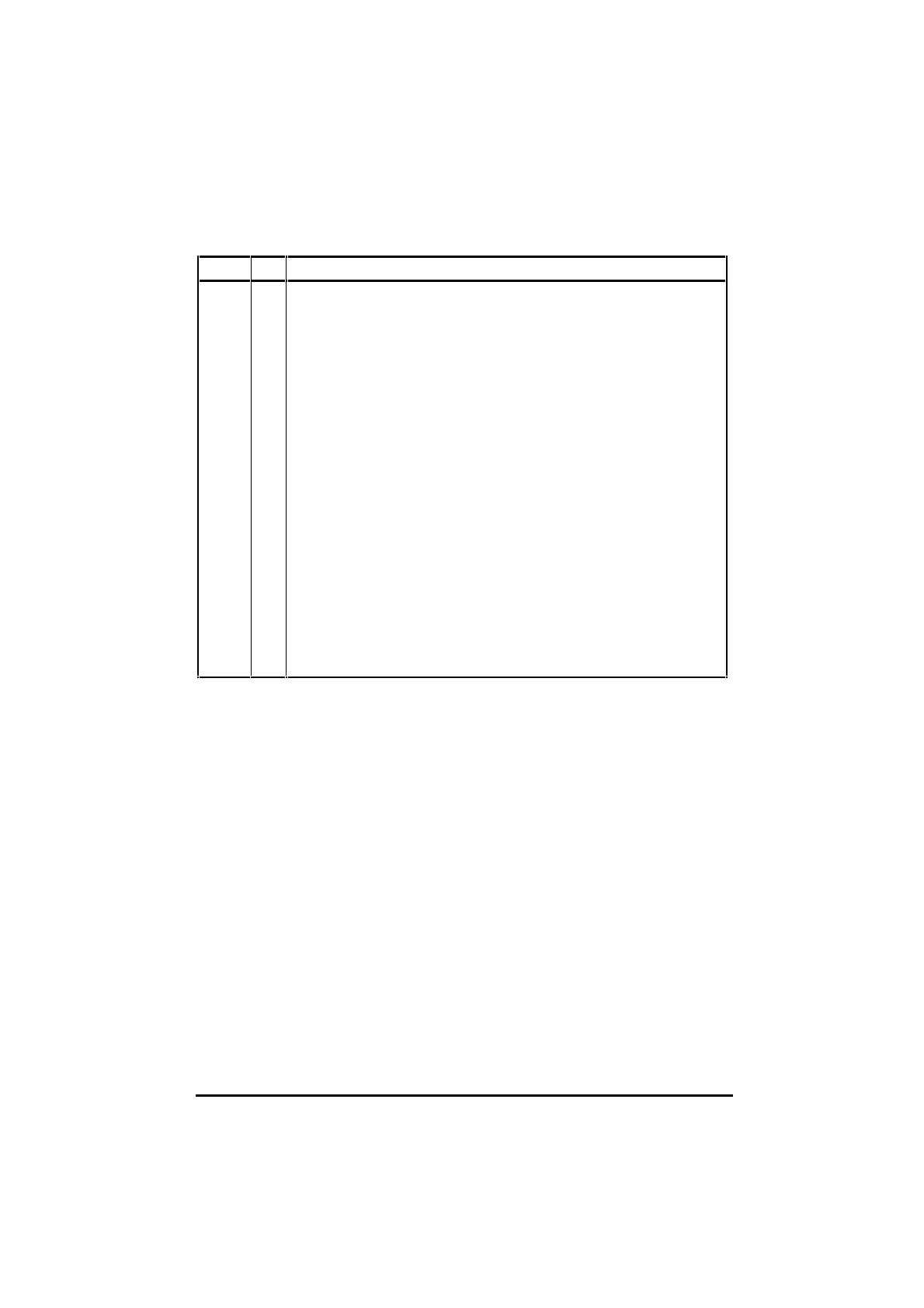

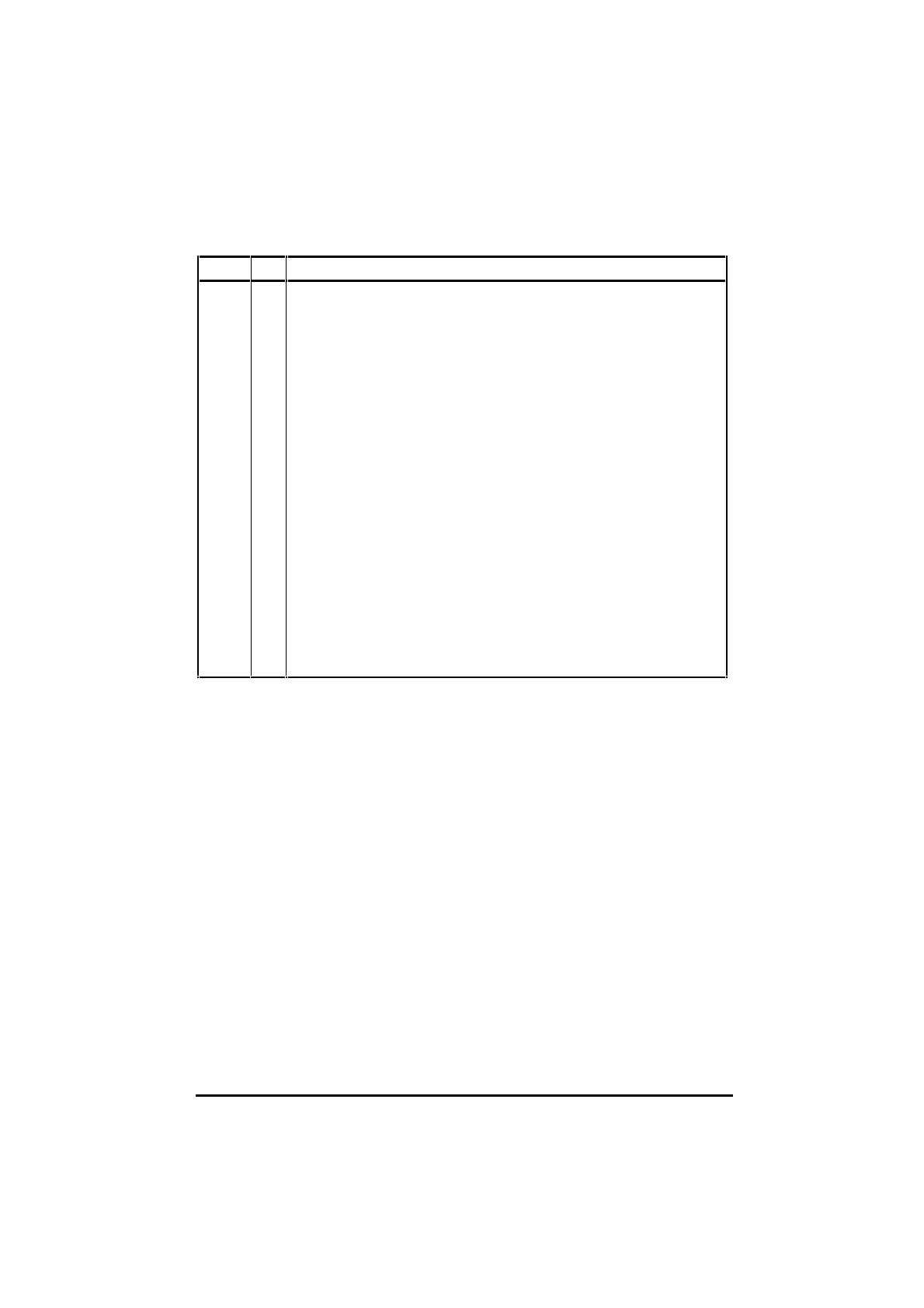

Bit Notes

5 ~ 7 M Timer mode

Mode 0 (000): Normal modeMode 0 (000): Normal mode

The internal clock source (4MHz or 500KHz) clocks the counter. The TI event flag is

set when the counter wraps-around.

Mode 1 (001): External modeMode 1 (001): External mode

The counter is clocked from an external source DIGIN0 (on the the –ve edge). The TI

flag is set when the counter wraps-around.

Mode 2 (010): Capture modeMode 2 (010): Capture mode

Capture mode. The counter is clocked by the internal clock source (4MHz or

500KHz). A 1 to 0 transition on DIGIN0 causes the current counter value to be

latched into the TIMER register, the counter is then reloaded with the RELOAD

register and the TI flag set. (Use #85.05 to read the timer value in mode 2, not

#85.03.)

Mode 3 (011): Trigger modeMode 3 (011): Trigger mode

The internal clock source (4MHz or 500KHz) clocks the counter. However the TI

event flag is set when a 1 to 0 transition is detected on DIGIN0, NOT when the

counter wraps-around. The reload mode works in the same way as mode 0 or 1.

Mode 4 (100): Gated modeMode 4 (100): Gated mode

The internal clock source (4MHz or 500KHz) clocks the counter; the count input is

gated by the DIGIN0 input (active low). The TI event flag is set when the counter

wraps-around.

Loading...

Loading...