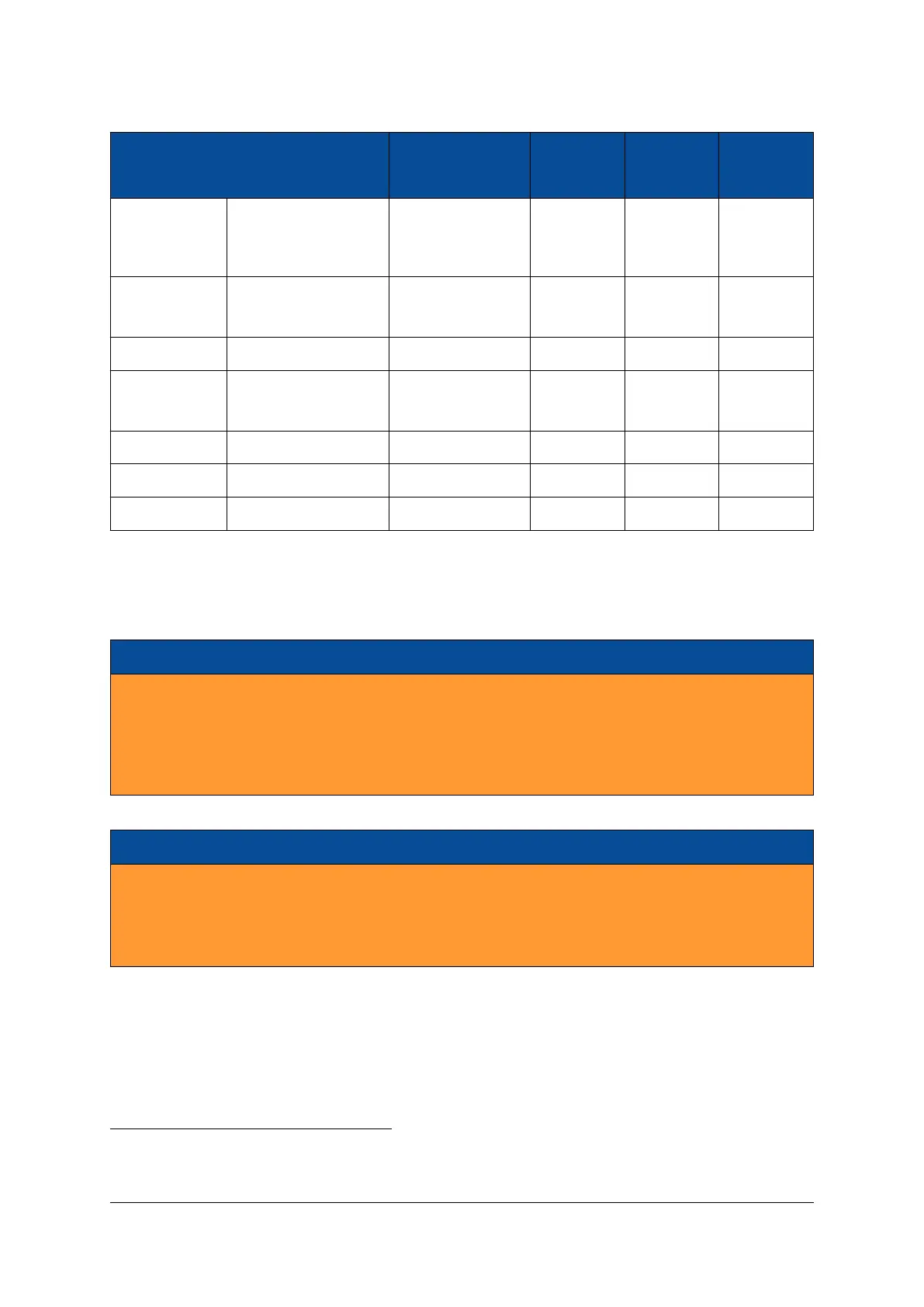

Signal Name MPSoC Pins Supported Connector Connector Connector

Voltages A Pins B Pins C Pins

VCC_CFG_MIO VCCO_PSIO1_501,

VCCO_PSIO3_503,

VCCO_BE

4

1.8 V - 3.3 V ±5% 74, 77 - -

VCC_IO_BE_BF VCCO_BE

4

,

VCCO_BF

4

1.2 V - 3.3 V ±5%

5

- - 76

VCC_IO_BO VCCO_BO

4

1.2 V - 3.3 V ±5%

5

41 - -

VCC_IO_BN VCCO_BN

4

,

VCCO_BF

4

1.2 V - 3.3 V ±5%

5

38 - -

VCC_IO_B64 VCCO_66 1.0 V - 1.8 V

6

±5% - - 116, 158

VCC_IO_B65 VCCO_65 1.0 V - 1.8 V ±5% - 64, 88, 140 -

VCC_IO_B66 VCCO_66 1.0 V - 1.8 V ±5% - 67, 95, 143 -

Table 9: VCC_IO Pins

Note that the I/Os on connector C from banks 65 and 66 are referenced to VCC_IO_B65 and VCC_IO_B66,

which are located on module connector B.

4 5 6

Warning!

Use only VCC_IO voltages compliant with the equipped MPSoC device; any other voltages may dam-

age the equipped MPSoC device, as well as other devices on the Mercury+ XU6 SoC module.

Do not leave a VCC_IO pin floating, as this may damage the equipped MPSoC device, as well as other

devices on the Mercury+ XU6 SoC module.

Warning!

Do not power the VCC_IO pins when PWR_GOOD and PWR_EN signals are not active. If the module

is not powered, you need to make sure that the VCC_IO voltages are disabled (for example, by using a

switch on the base board, which uses PWR_GOOD as enable signal). Figure 10 illustrates the VCC_IO

power requirements.

4

For HD I/O banks generic supply names are used - refer to Section 2.9.4 for details on I/O banks connectivity and supplies.

5

For voltages of 3.3 V for VCC_IO_BE_BF, VCC_IO_BO and VCC_IO_BN the tolerance range is -5% to +3%.

6

If the level shifted signals described in Table 7 are used, a minimum voltage of 1.2 V is required for VCC_IO_B64.

D-0000-464-001 24 / 58 Version 02, 21.07.2021

Loading...

Loading...