44x/EN PL/Hb6

-52 MiCOM 40 Agile

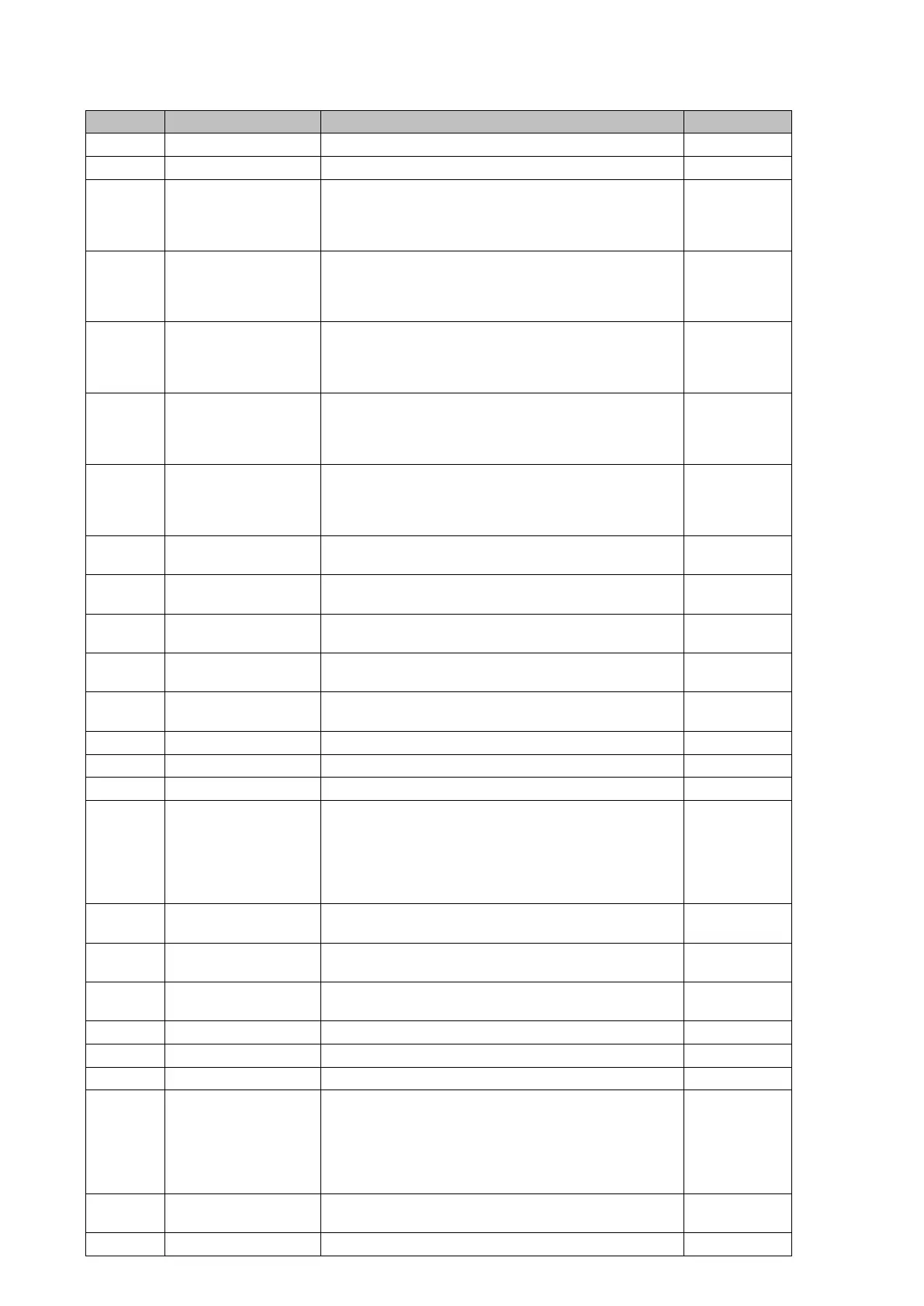

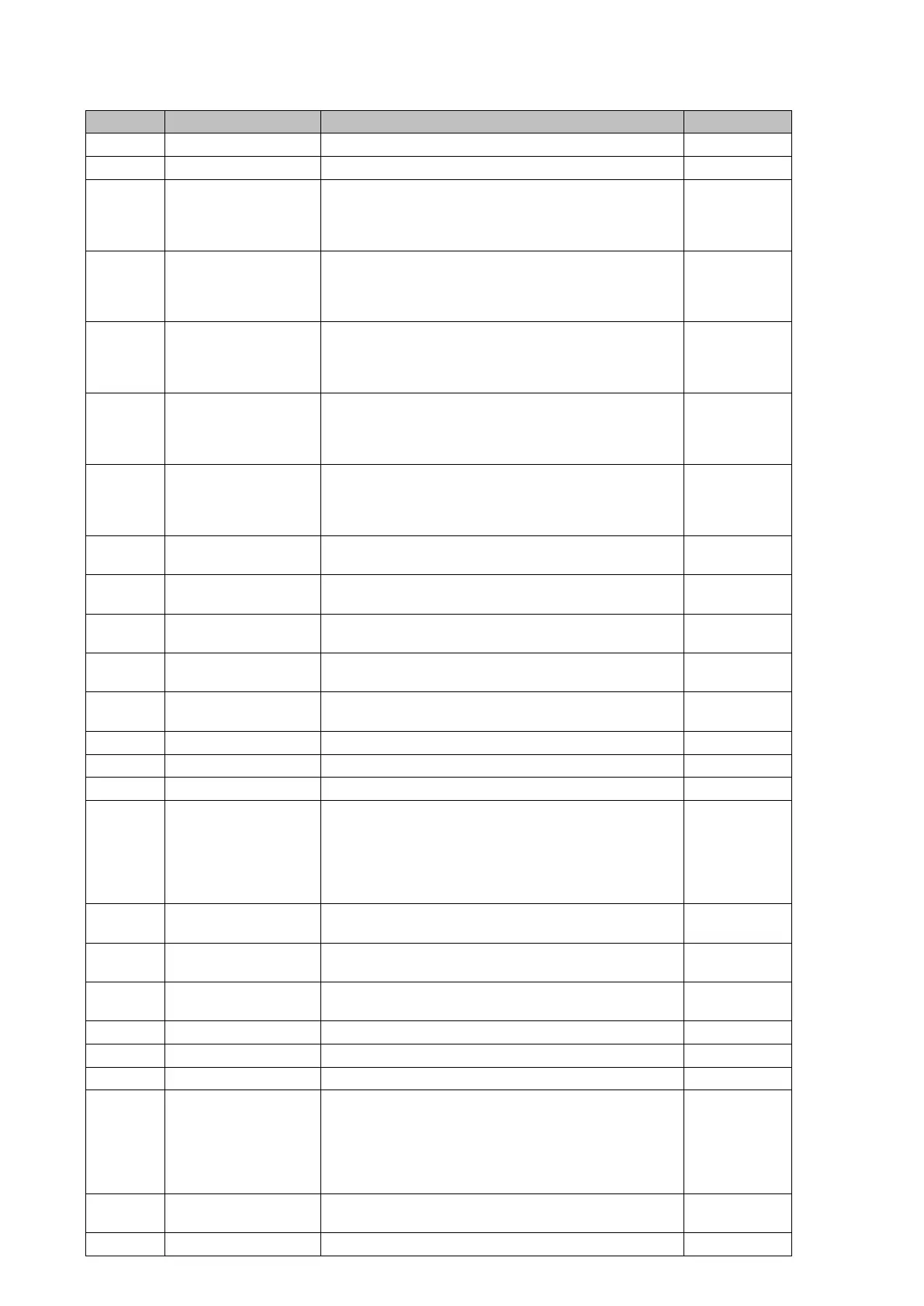

Ordinal English Text Description Source

395 Tzq Timer in zone Q elapsed (at 1 = end of timer) PSL

1097 TZq Timer Block Timer block TZq input PSL

1084 User Trip A

Internal input for trip logic A

Set to 1: Trip A Internal input managed with the

general trip logic(with A/R / Evolving fault…)

Can be assigned by external condition

PSL (IN) Trip

Logic

1085 User Trip B

Internal input for trip logic B

Set to 1: Trip B Internal input managed with the

general trip logic(with A/R / Evolving fault…)

Can be assigned by external condition

PSL (IN)

Trip Logic

1086 User Trip C

Internal input for trip logic C

Set to 1: Trip C Internal input managed with the

general trip logic(with A/R / Evolving fault…)

Can be assigned by external condition

PSL (IN)

Trip Logic

239 V< Dead Bus

Dead Bus: high when the Dead Bus condition is met

(voltage below the V<Dead Bus threshold value

(setting) - always calculated as a single phase voltage

reference.

PSL (OUT)

Synchro

Check

237 V< Dead Line

Dead Line: high when the Dead Line condition is met

(voltage below the 'V< Dead Line' threshold value

(setting) – The measured voltage is always calculated

as a single phase voltage

PSL (OUT)

Synchro

Check

285 V< Start Any A Any undervoltage start detected on phase A

PSL (OUT)

Undervoltage

286 V< Start Any B Any undervoltage start detected on phase B

PSL (OUT)

Undervoltage

287 V< Start Any C Any undervoltage start detected on phase C

PSL (OUT)

Undervoltage

197 V<1 Alarm 1st stage undervoltage alarm picks up when V<1 starts

PSL (OUT)

V<1

288 V<1 Start Undervoltage 1

st

stage start (any phase)

PSL (OUT)

Undervoltage

371 V<1 Start A Undervoltage stage 1 pick up on phase A PSL

372 V<1 Start B Undervoltage stage 1 pick up on phase B PSL

373 V<1 Start C Undervoltage stage 1 pick up on phase C PSL

1069 V<1 Timer Block

Block phase undervoltage stage 1 time delay

Set to 1: 'V<1 Time Delay' will be blocked and V<1 will

start but will not issue any trip command.

Reset to 0: Opto input power off if signal assigned to

an opto input OR DDB at 0 if signal assigned to a DDB

cell

PSL (IN) V<1

290 V<1 Trip Undervoltage 1

st

stage – 3-phase trip

PSL (OUT)

Undervoltage

198 V<2 Alarm

2nd stage undervoltage alarm picks up when V<21

starts

PSL (OUT)

V<2

289 V<2 Start Undervoltage 2

nd

stage start (any phase)

PSL (OUT)

Undervoltage

374 V<2 Start A Undervoltage stage 2 pick up on phase A PSL

375 V<2 Start B Undervoltage stage 2 pick up on phase B PSL

376 V<2 Start C Undervoltage stage 2 pick up on phase C PSL

1070 V<2 Timer Block

Block phase undervoltage stage 2 time delay

Set to 1: 'V<2 Time Delay' will be blocked and V<1 will

start but will not issue any trip command.

Reset to 0: Opto input power off if signal assigned to

an opto input OR DDB at 0 if signal assigned to a DDB

cell

PSL (IN) V<2

291 V<2 Trip Undervoltage stage 2

nd

stage – 3-phase trip

PSL (OUT)

Undervoltage

396 V<3 Start Undervoltage stage 3 start PSL

Loading...

Loading...