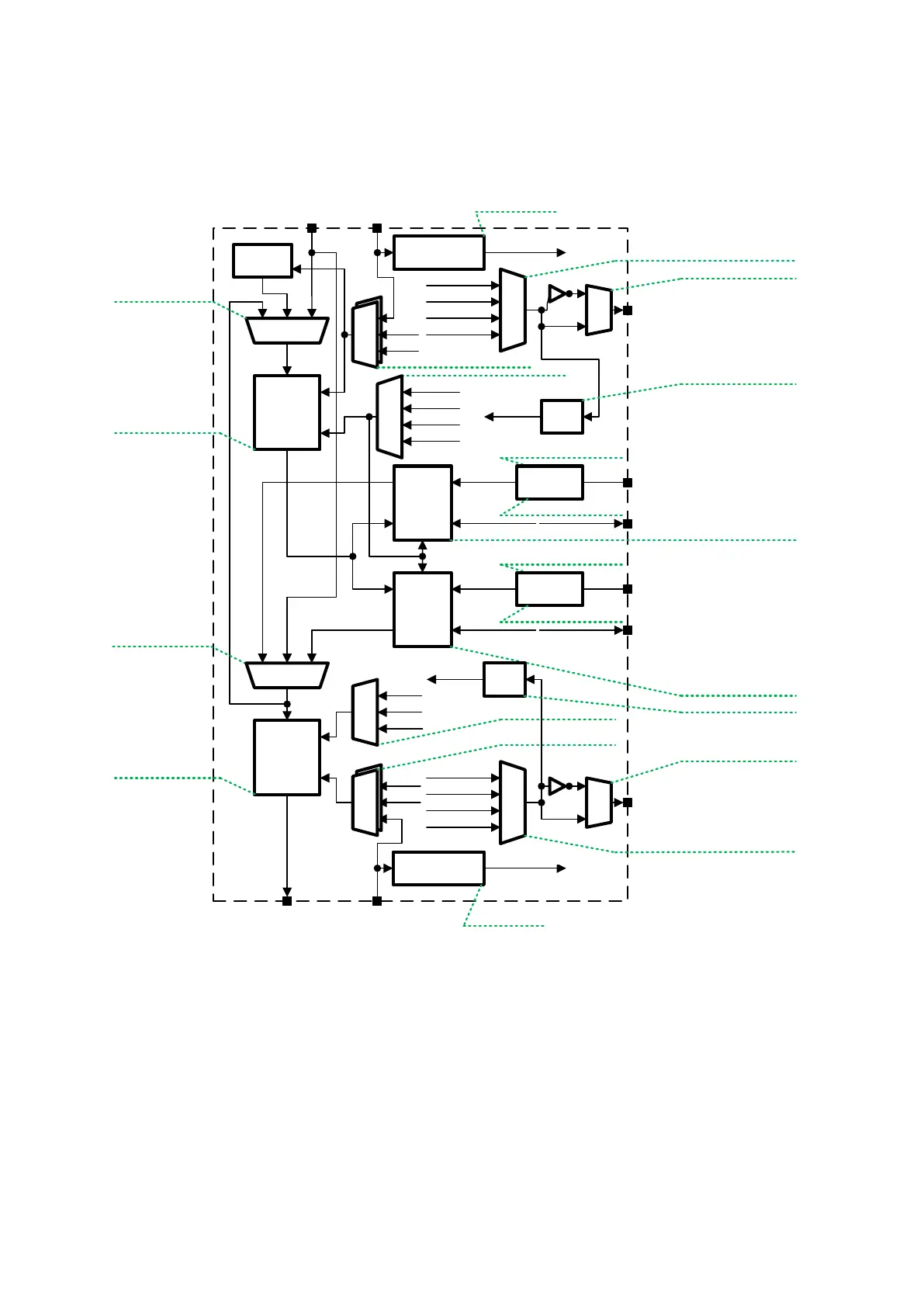

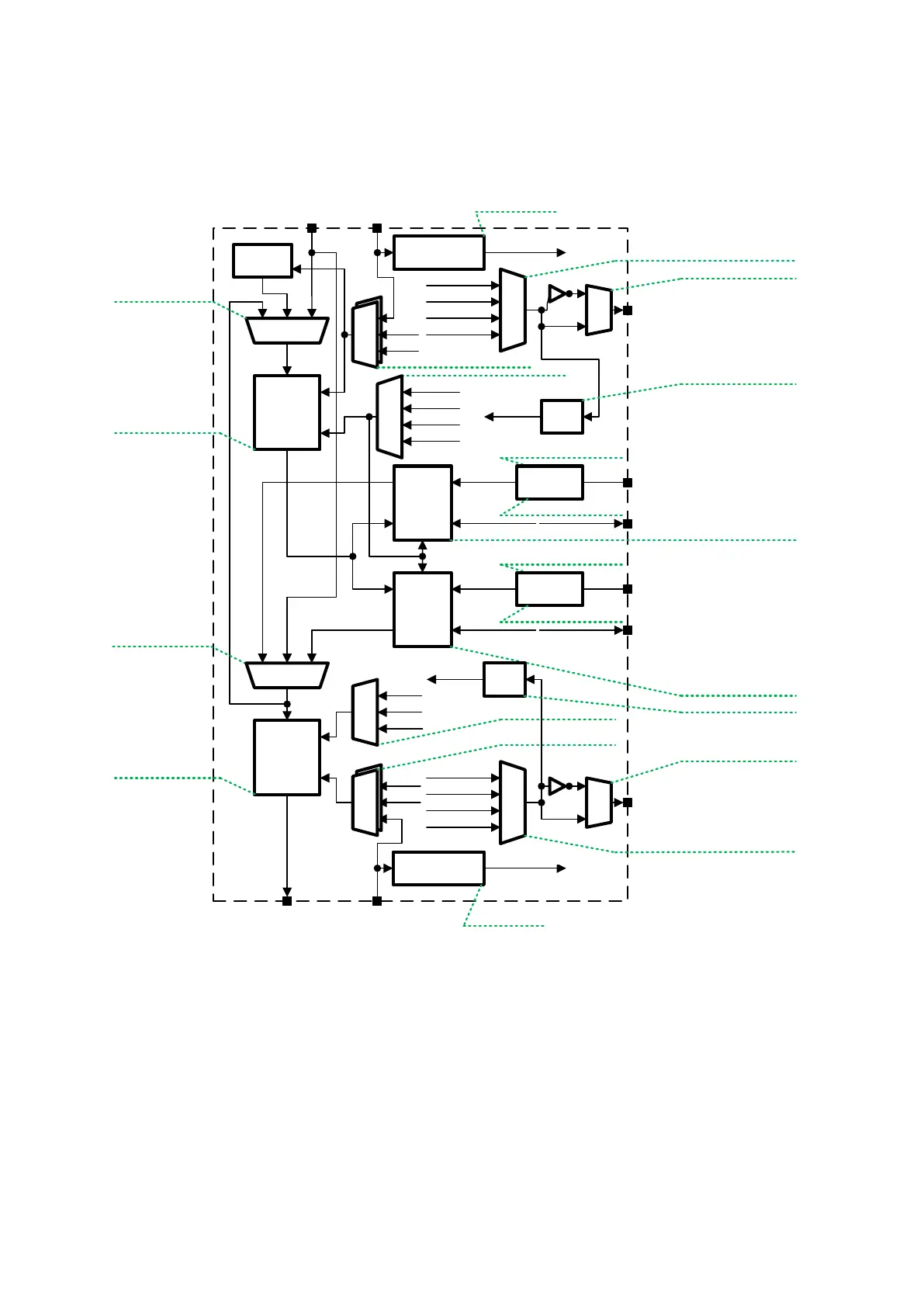

FCLK2_DLY (0x002A[15:14])

FCLK1_DLY (0x002A[13:12])

mclk1i

MCLK2_INV (0x002B[9])

txclkdivided

rxclkdivided

txtspclkA

rxtspclkA

MCLK1_INV (0x002B[8])

rxclkdivided

txtspclkA

rxtspclkA

txclkdivided

mclk2dly

MCLK_1DLY (0x002B[11:10])

mclk1dly

fclk2i

fclk1i

FCLK1_INV (0x002B[14])

FCLK2_INV (0x002B[15])

fclk2i

fclk1i

rxtspclk(A/B)

SRST_RXFIFO (0x0020[7])

SRST_TXFIFO (0x0020[6])

MCLK2_DIV (0x002C[15:8])

MCLK2_EN (0x002B[0])

MCLK2_SRC (0x002B[5:4])

TXRDCLK_MUX (0x002A[7:6])

RX_MUX (0x002A[11:10])

frxai

mclk1

mclk1dly

mclk2dly

fclk2i

fclk1i

Data from

RxTSP(A/B)

Data to

TxTSP(A/B)

txtspclk(A/B)

fclk2i

fclk1i

Lime

Light

PORT2

(def: RF2BB)

Lime

Light

PORT1

(def: BB2RF)

RX_MUX

fclk2

fclk1

/

/

DIQ2 /

Control

DIQ1 /

Control

DIV by 2÷512

(even numbers)

rxtspclk(A/B)

fclk2i

fclk1i

DIV by 2÷512

(even numbers)

TXFIFO

rdclk(A/B)

wrclk

RXFIFO

wrclk(A/B)

rdclk

mclk2

lmlaio1

lmlaio2

01

MUX

0

1

2

MUX

0

1

2

LML2_TRXIQPULSE (0x0022[15])

LML2_SISODDR (0x0022[14])

LML2_FIDM (0x0023[5])

LML2_TXNRXIQ (0x0023[4])

LML2_MODE (0x0023[3])

LML2_S3S (0x0027[15:14])

LML2_S2S (0x0027[13:12])

LML2_S1S (0x0027[11:10])

LML2_S0S (0x0027[9:8])

LML2_BQP (0x0027[7:6])

LML2_BIP (0x0027[5:4])

LML2_AQP (0x0027[3:2])

LML2_AIP (0x0027[1:0])

LML2_BB2RF_PST (0x0028[12:8])

LML2_BB2RF_PRE (0x0028[4:0])

LML2_RF2BB _PST (0x0029[12:8])

LML2_RF2BB_PRE (0x0029[4:0])

LML1_TRXIQPULSE (0x0022[13])

LML1_SISODDR (0x0022[12])

LML1_FIDM (0x0023[2])

LML1_TXNRXIQ (0x0023[1])

LML1_MODE (0x0023[0])

LML1_S3S (0x0027[15:14])

LML1_S2S (0x0027[13:12])

LML1_S1S (0x0027[11:10])

LML1_S0S (0x0027[9:8])

LML1_BQP (0x0024[7:6])

LML1_BIP (0x0024[5:4])

LML1_AQP (0x0024[3:2])

LML1_AIP (0x0024[1:0])

LML1_BB2RF_PST (0x0025[12:8])

LML1_BB2RF_PRE (0x0025[4:0])

LML1_RF2BB_PST (0x0026[12:8])

LML1_RF2BB_PRE (0x0026[4:0])

TX_MUX (0x002A[9:8])

TXWRCLK_MUX (0x002A[4:5])

RXRDCLK_MUX (0x002A[3:2])

RXWRCLK_MUX (0x002A[1:0])

rxclkdivided

txclkdivided

MUX

0

1

2

3

MUX

0

1

2

3

MCLK1SRC (0x002B[3:2])

MCLK1_DIV (0x002C[7:0])

MCLK1_EN (0x002B[1])

2

RNDGEN

TX_MUX

01 2

MUX

0

2

1

Delay

Delay

MCLK2_DLY (0x002B[13:12])

MUX

1

0

MUX

0

1

2

3

MUX

1

0

mclk2i

Delay and

inversion

Delay and

inversion

Loading...

Loading...