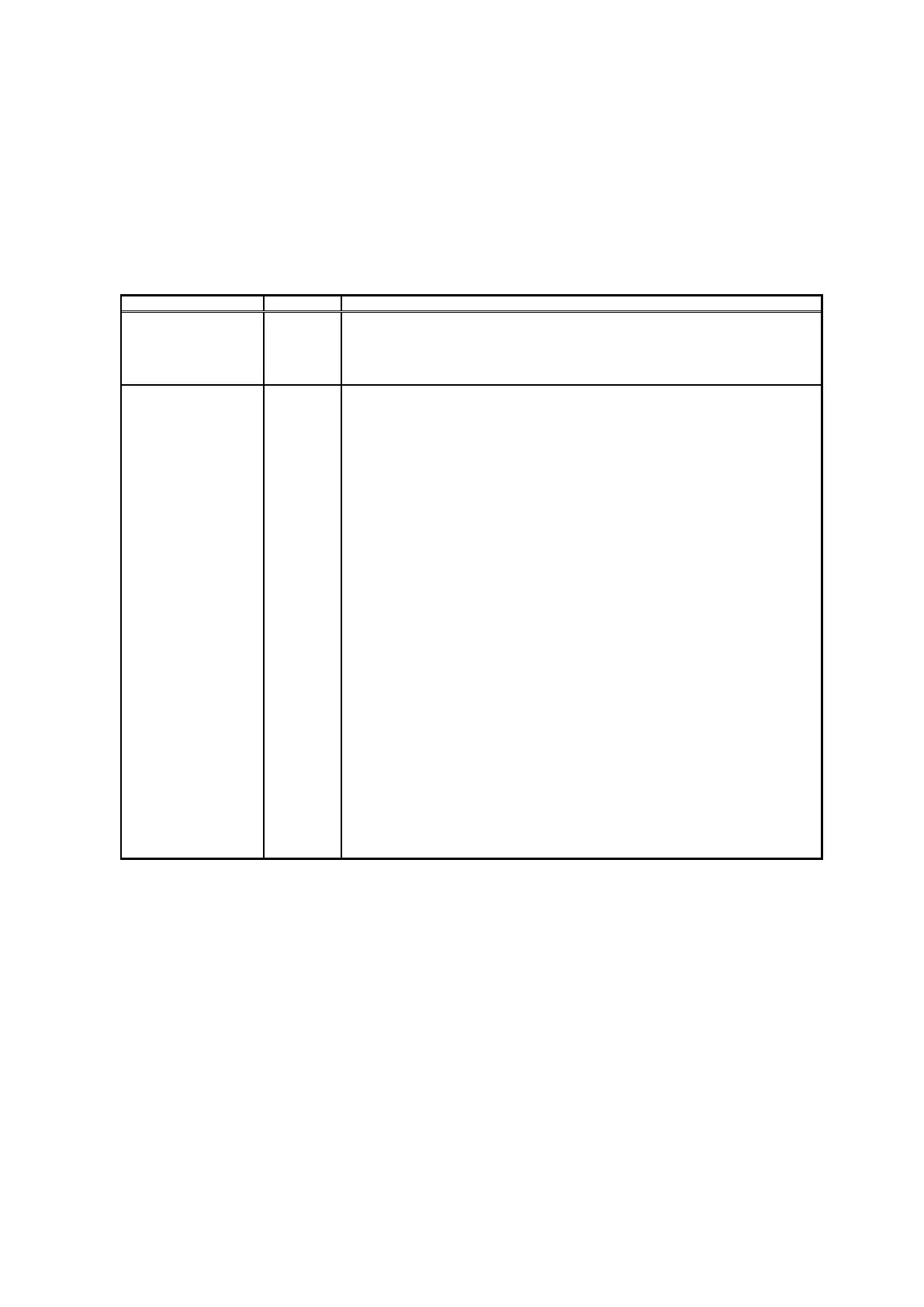

describe the control registers of the BIAS module.

Reserved

MUX_BIAS_OUT[1:0]: Test mode of the BIAS_TOP

0 – NO test mode (default)

1 – vr_ext_bak and vr_cal_ref=600mV is passed to the ADC input MUX.

Vr_ext_bak is the voltage read on the off-chip 10Kohm reference resistor. Ip60f is

connected to r_ext=10kOhm and RP_CALIB_BIAS is changed until vr_ext becomes

600mV.

2 – Vptat_600mV and vr_cal_ref=600mV is passed to the ADC input

MUX. The ratio between the two will be proportional to absolute temp.

3 – No test mode

RP_CALIB_BIAS[4:0]: Calibration code for rppolywo. This code is set by the

calibration algorithm: BIAS_RPPOLY_calibration Default: 16

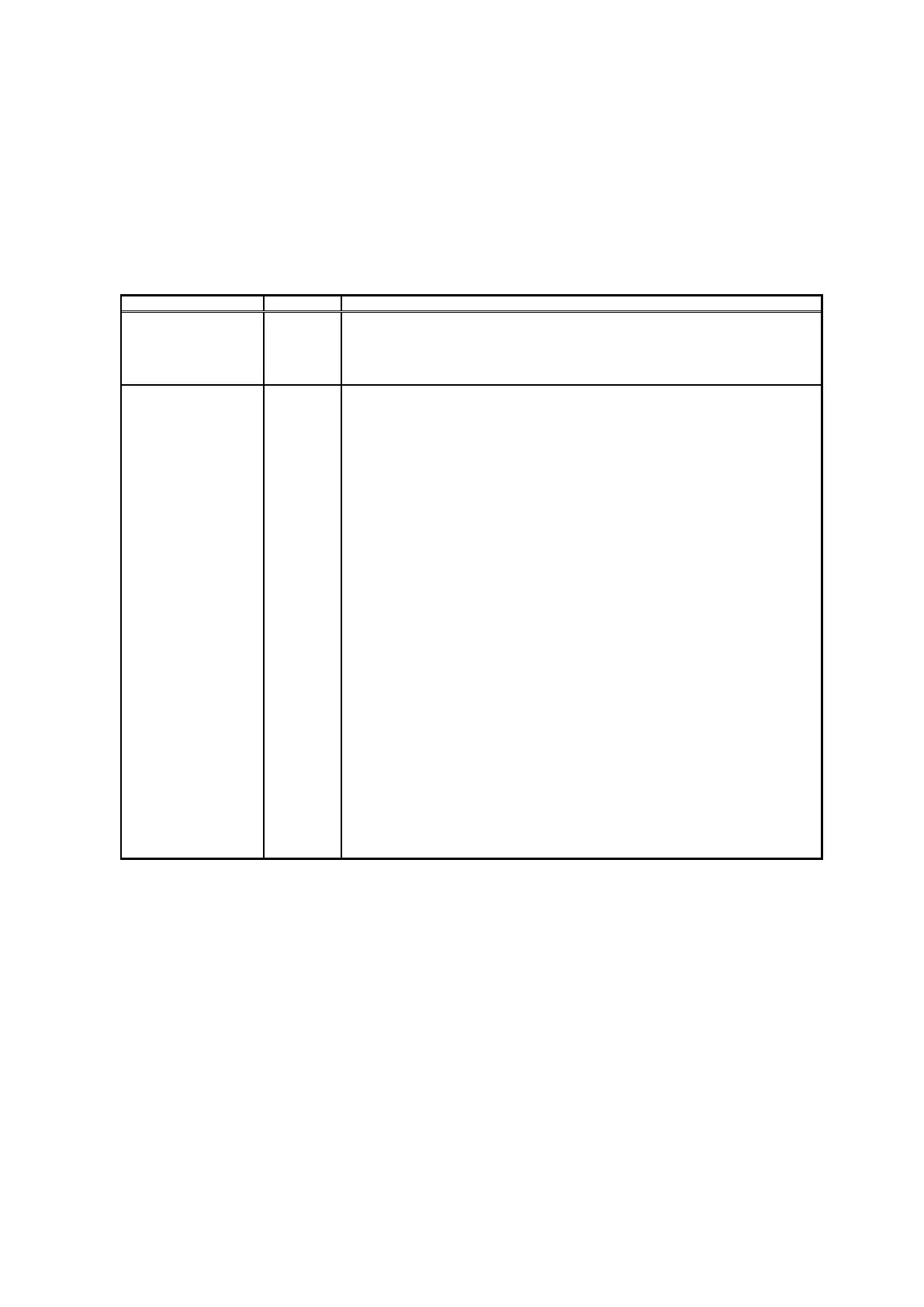

Reserved

PD_FRP_BIAS: Power down signal for Fix/RP block

0 – Enabled (default)

1 – Powered down

PD_F_BIAS: Power down signal for Fix

0 – Enabled (default)

1 – Powered down

PD_PTRP_BIAS: Power down signal for PTAT/RP block

0 – Enabled (default)

1– Powered down

PD_PT_BIAS: Power down signal for PTAT block

0 – Enabled (default)

1 – Powered down

PD_BIAS_MASTER: Enable signal for central bias block

0 – Sub blocks may be selectively powered down (default)

1 – Poweres down all BIAS blocks

Default: 00000100 00000000

Loading...

Loading...