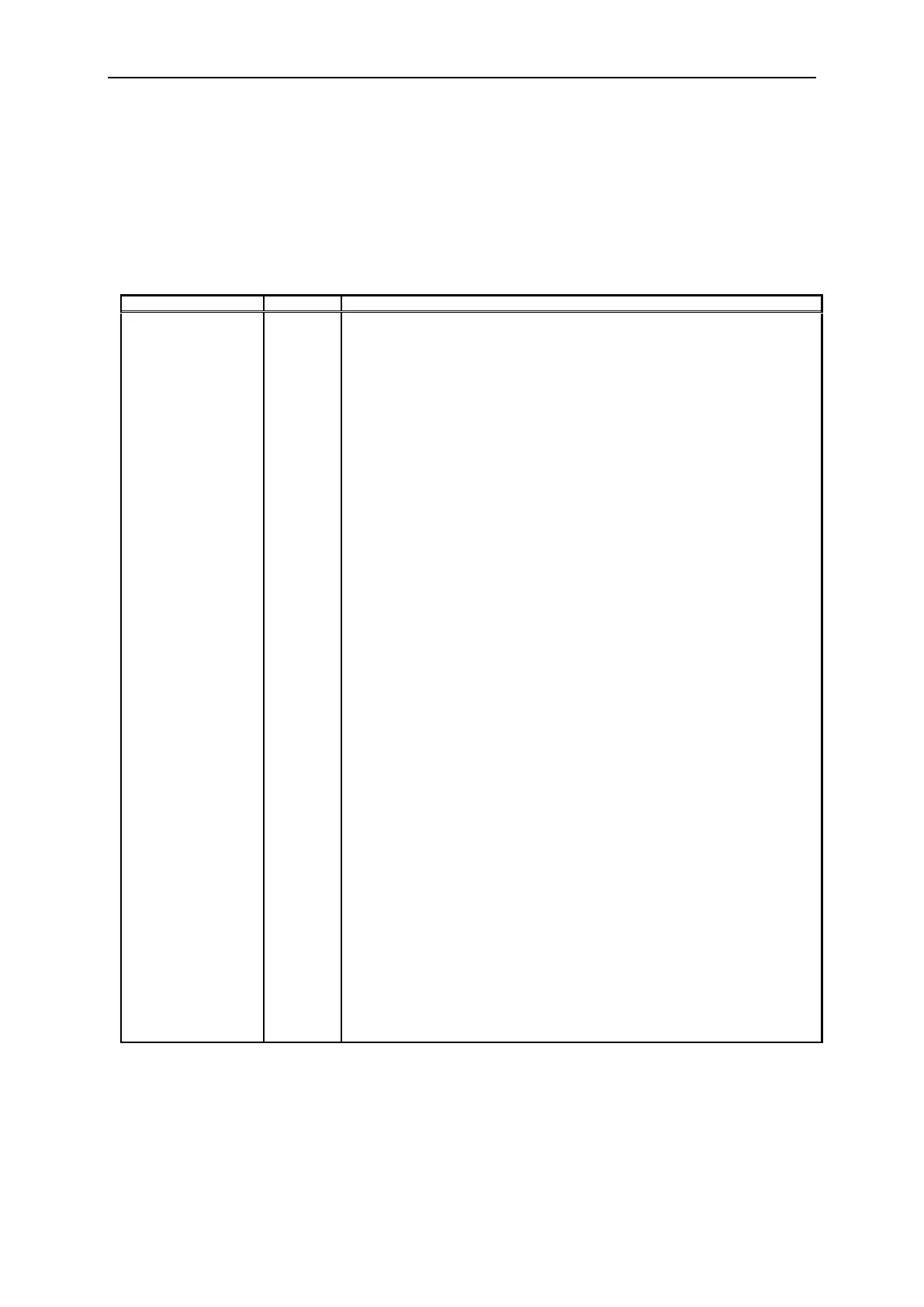

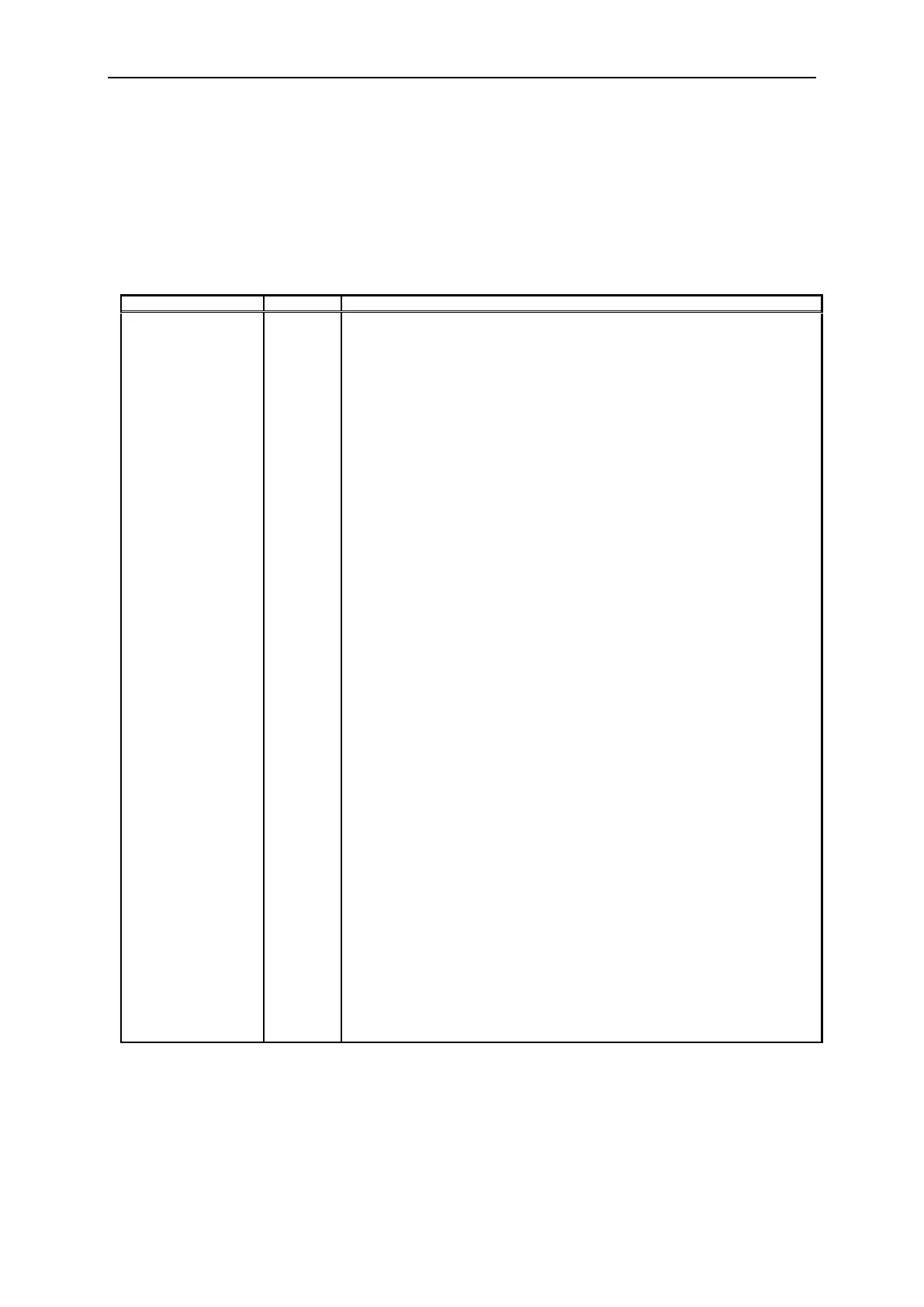

control registers of the LDO modules.

EN_LDO_DIG: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIGGN: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIGSXR: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIGSXT: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIVGN: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIVSXR: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_DIVSXT: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_LNA12: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_LNA14: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_MXRFE: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_RBB: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_RXBUF: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_TBB: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_TIA12: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_LDO_TIA14: Enables the LDO

0 – Powered down (default)

1 – Enabled

EN_G_LDO: Enable control for all the LDO power downs

0 – All LDO modules powered down

1 – All LDO modules controlled by individual power down registers

(default)

Default: 00000000 00000001

Loading...

Loading...