RxTSPA and RxTSPB modules.

shown in Figure 26.

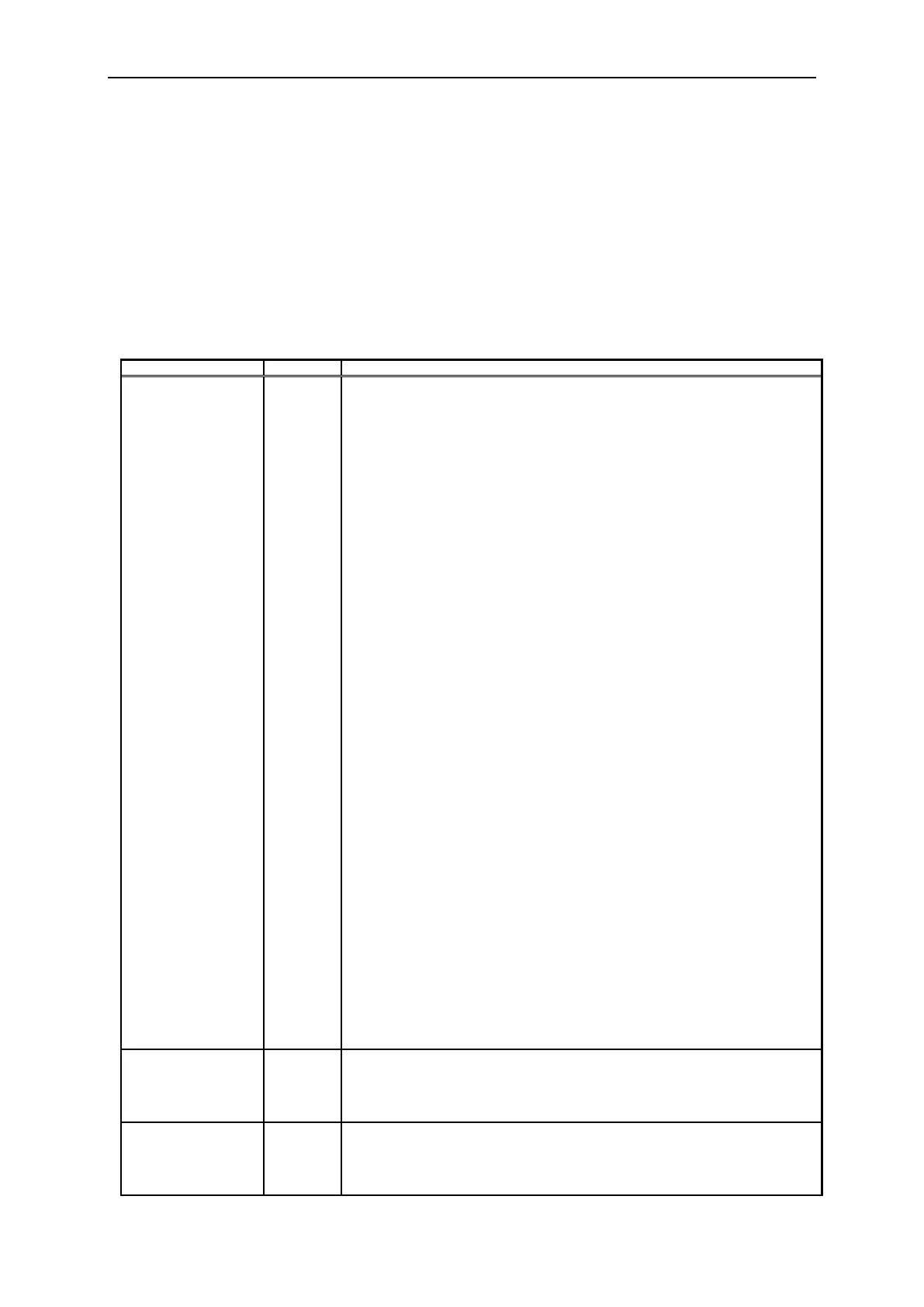

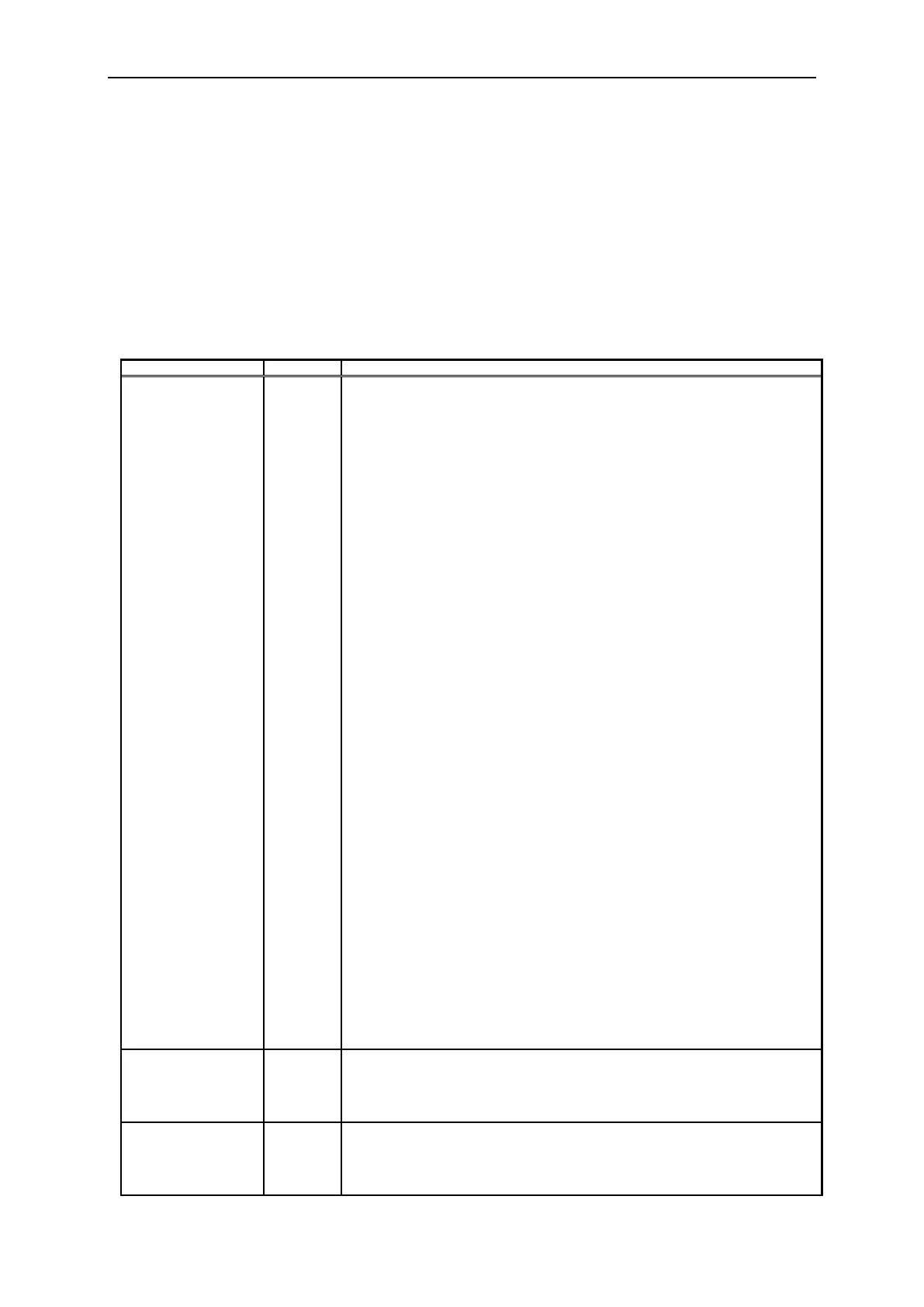

CAPTURE: Captures value, selected by CAPSEL[1:0].

0 – (default)

0-to-1 – positive edge captures value, selected by CAPSEL[1:0]

CAPSEL[1:0]: Selects what parameters to capture to memory (addresses 0x0400E

and 0x0400F)

00 – RSSI (default)

01 – ADCI and ADCQ (see CAPSEL_ADC register for more information)

10 – BSIGI and BSTATE

11 – BSIGQ and BSTATE

CAPSEL_ADC: Selects ADC value source to be captured, when CAPSEL[1:0] = 01.

0 – RxTSP input (default)

1 – RxTSP output

Reserved

TSGFC: TSG full scale control.

0 – -6dB (default)

1 – Full scale

TSGFCW[1:0]: Set frequency of TSG's NCO.

DC TSG NCO frequency

========================

00 do not use

01 TSP clk/8 (default)

10 TSP clk/4

11 do not use

TSGDCLDQ: Load TSG DC Q register with value from DC_REG[15:0].

0 – No action (default)

0-to-1 – positive edge loads TSG's DC register Q.

TSGDCLDI: Load TSG DC I register with value from DC_REG[15:0].

0 – No action (default)

0-to-1 – positive edge loads TSG's DC register I.

TSGSWAPIQ: Swap signals at test signal generator's output.

0 – Do not swap (default)

1 – Swap I an Q signal sources comming from TSG

TSGMODE: Test signal generator mode.

0 – NCO (default)

1 – DC source

INSEL: Input source of TxTSP:

0 – LML output (default)

1 – Test signal generator

BSTART: Starts delta sigma built in self test. Keep it at 1 one at least three clock

cycles.

0 – (default)

0-to-1 – positive edge activates BIST

EN: RxTSP modules enable.

0 – Disabled

1 – Enabled (default)

Default: 00000000 10000001

Reserved

GCORRQ[10:0]: Gain corrector value, channel Q. Unsigned integer.

Possible values are 0 – 2047, default is 2047

Default: 00000111 11111111

Reserved

GCORRI[10:0]:Gain corrector value, channel I Unsigned integer.

Possible values are 0 to 2047, default is 2047

Default: 00000111 11111111

Loading...

Loading...