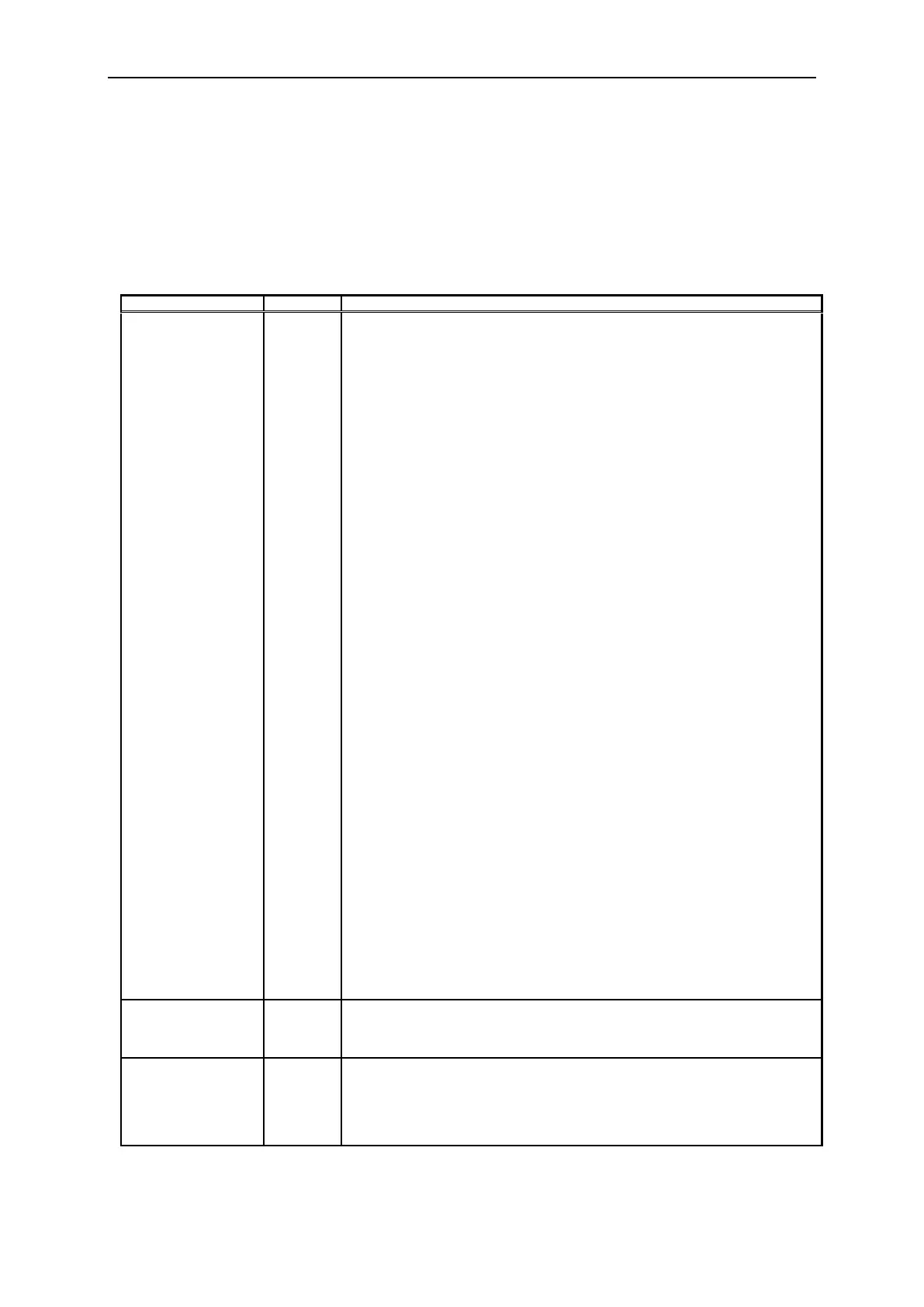

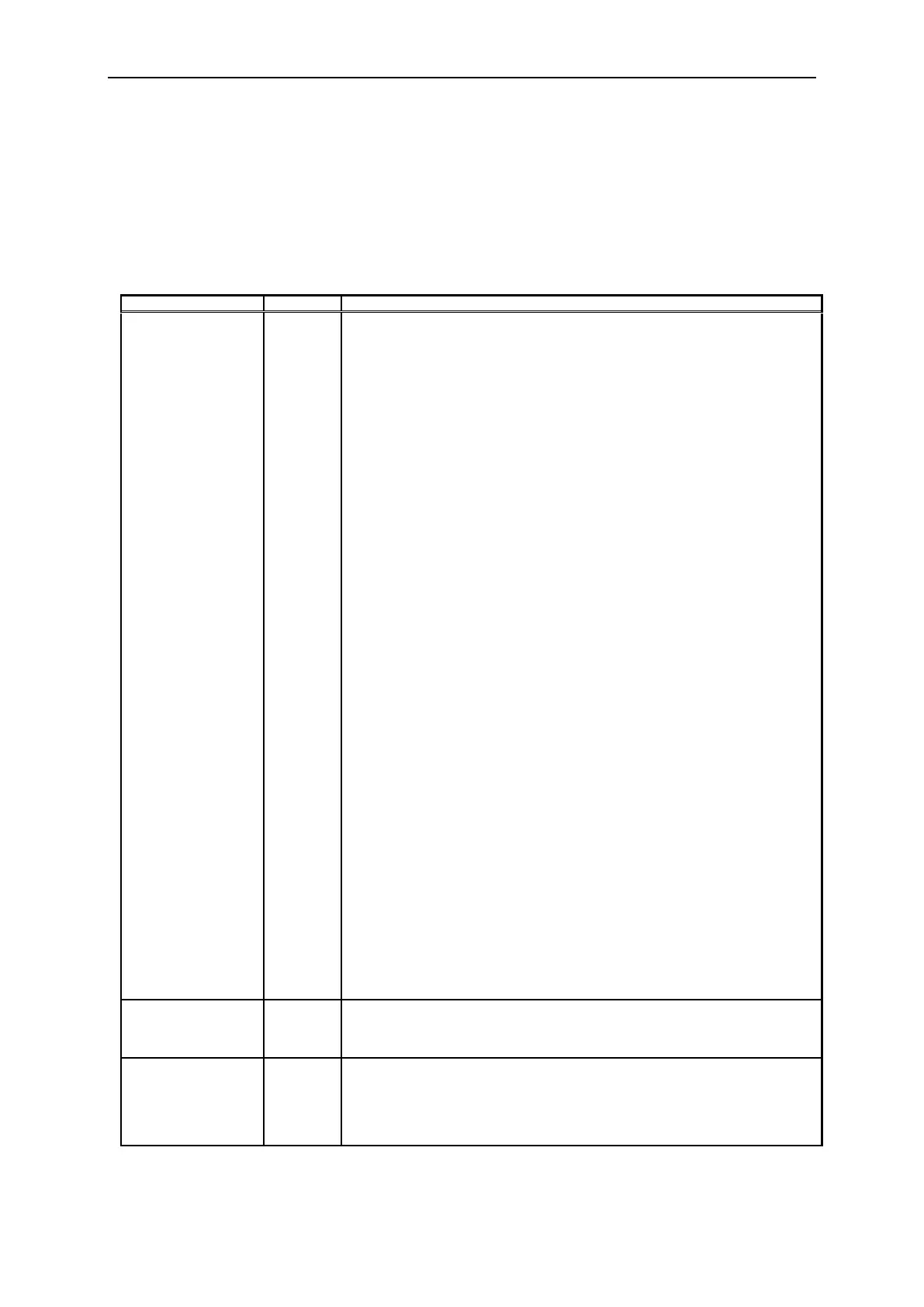

describes the control registers of the CGEN module.

SPDUP_VCO_CGEN: Bypasses the noise filter resistor for fast settling time. It

should be connected to a 1us pulse.

0 – speed up disabled (noise filter resistor active) (default)

1 – speed up enabled (noise filter resistor shorted)

RESET_N_CGEN: Resets SX. A pulse should be used in the start-up to reset.

0 – Reset

1 – Normal operation (default)

Reserved

EN_ADCCLKH_CLKGN: Selects if F_CLKH or F_CLKL is connected to FCLK_ADC

(F_CLKH and F_CLKL are the two internally generated clocks. A MUX will connect

one of them to FCLK_ADC and the other to FCLK_DAC.).

0 – FCLK_ADC from F_CLKH / FCLK_DAC from F_CLKL

1 – FCLK_ADC from F_CLKL / FCLK_DAC from F_CLKH (default)

EN_COARSE_CKLGEN: Enable signal for coarse tuning block.

0 – Coarse tuning disabled (default)

1 – Coarse tuning enabled

EN_INTONLY_SDM_CGEN: Enables INTEGER-N mode of the SX.

0 – Frac-N mode (default)

1 – INT-N mode

EN_SDM_CLK_CGEN: Enables/Disables SDM clock. In INT-N mode or for noise

testing, SDM clock can be disabled.

0 – SDM clock disabled

1 – SDM clock enabled (default)

Reserved

PD_CP_CGEN: Power down for Charge Pump.

0 – block active (default)

1 – block powered down

PD_FDIV_FB_CGEN: Power down for feedback frequency divider.

0 – block active (default)

1 – block powered down

PD_FDIV_O_CGEN: Power down for forward frequency divider of the CGEN block.

0 – block active (default)

1 – block powered down

PD_SDM_CGEN: Power down for SDM.

0 – block active (default)

1 – block powered down

PD_VCO_CGEN: Power down for VCO.

0 – block active

1 – block powered down (default)

PD_VCO_COMP_CGEN: Power down for VCO comparator.

0 – block active (default)

1 – block powered down

EN_G_CGEN: Enable control for all the CGEN power downs.

0 – All CGEN modules powered down

1 – All CGEN modules controlled by individual power down registers

(default)

Default: 01001001 00000101

Loading...

Loading...