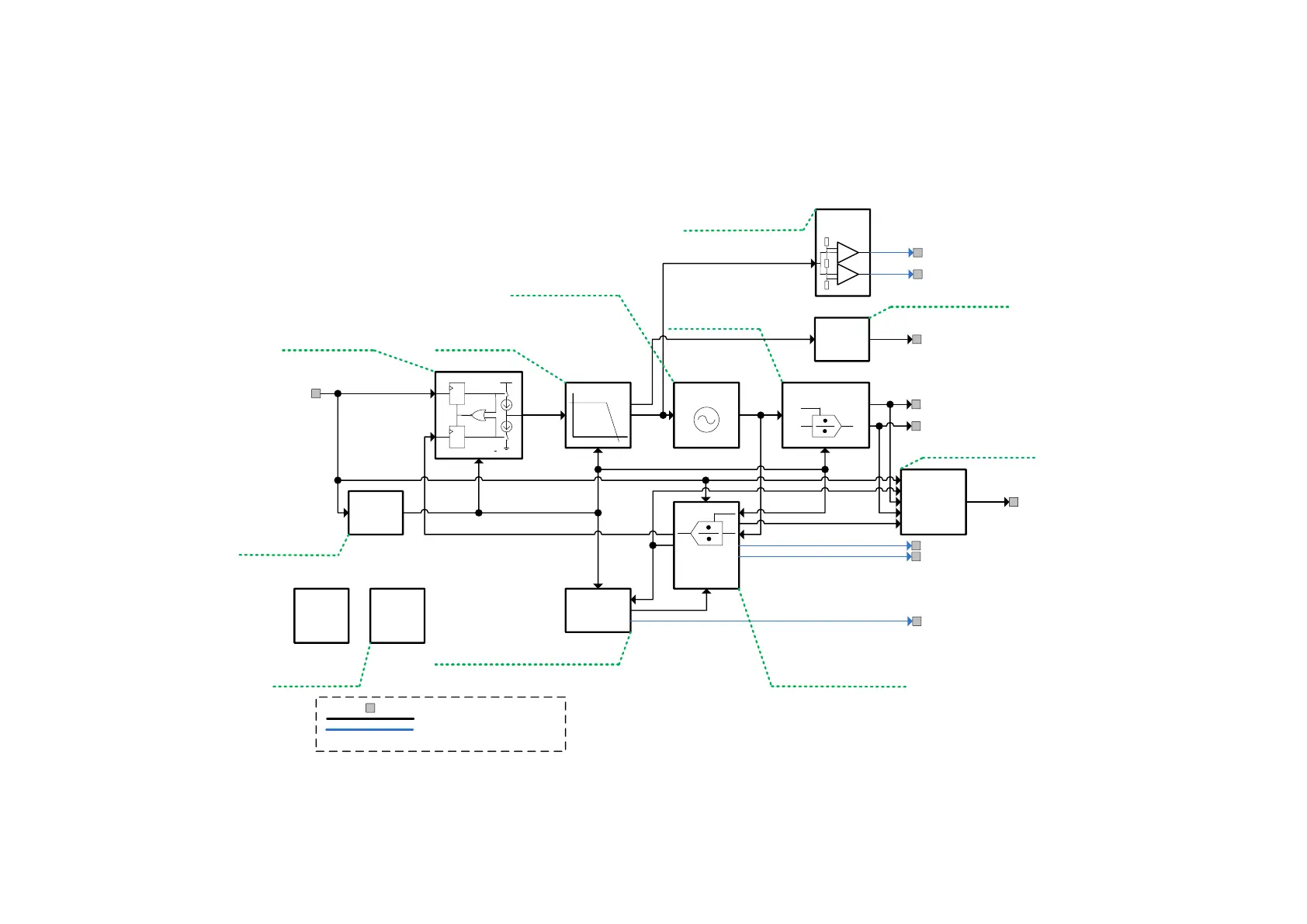

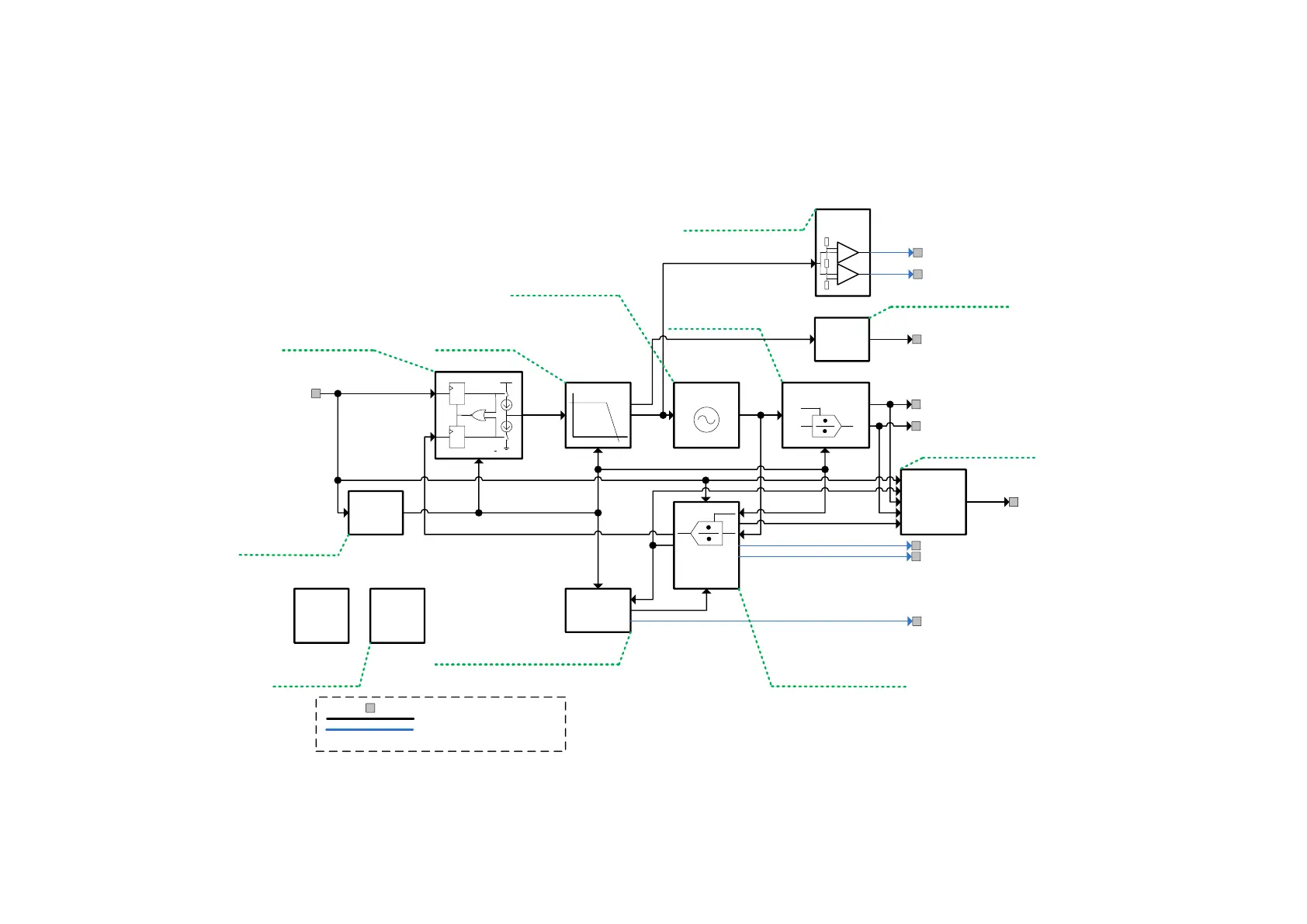

Forward divider

2^N

VCO

feedback

divider

Fractional

PFD

CP

LPF

Reset

signal

SYNC

SDM

ΣΔ

Vtune

Comparator

LPF test

muxer

Test signal

muxers

To SPI: COARSEPLL_COMPO_CGEN (0x008C[14])

To SPI: COARSE_STEPDONE_CGEN (0x008C[15])

To: tstdo<1:0> (PAD)

To: tstao (PAD)

To SPI: VCO_CMPHO_CGEN (0x008C[13])

To SPI: VCO_CMPLO_CGEN (0x008C[12])

To SPI: SDM_TSTO_CGEN<13:0>

PD_CP_CGEN (0x0086[6])

REVPH_PFD_CGEN (0x008A[12])

IOFFSET_CP_CGEN<5:0> (0x008A[11:6])

IPULSE_CP_CGEN<5:0> (0x008A[5:0])

CP3_PLL_CGEN<3:0> (0x008C[7:4])

EN

_

COARSEPLL

_

CGEN

(

0

x

0086

[

10

])

CPZ_PLL_CGEN<3:0> (0x008C[3:0])

CP2_PLL_CGEN<3:0> (0x008C[11:8])

From: XCLK_RX (XBUF RX)

RESET_N_CGEN (0x0086[14])

EN_INTONLY_SDM_CGEN (0x0086[9])

EN_SDM_TSTO_CGEN (0x00A8[4])

SX_DITHER_EN_CGEN (0x0089[13])

FRAC_SDM_CGEN<19:0> (0x0087[15:0])+(0x0088[3:0])

INT

_

SDM

_

CGEN

<9

:

0

>

(

0

x

0088

[

13

:

4

])

REV_SDMCLK_CGEN (0x0089[15])

SEL_SDMCLK_CGEN (0x0089[14])

EN_SDM_CLK_CGEN (0x0086[8])

PD_SDM_CGEN (0x0086[3])

PD_VCO _CGEN (0x0086[1])

SPDUP_VCO_CGEN (0x0086[15])

ICT_VCO_CGEN<7:0> (0x008B[13:9])

CSW_VCO_CGEN<7:0> (0x008B[8:1])

PD_FDIV_FBCGEN (0x0086[5])

COARSE_START_CGEN (0x008B[0])

DIV_OUTCH_CGEN<7:0> (0x0089[10:3])

PD_VCO_COMP_CGEN (0x0086[1])

TST_CGEN<2:0> (0x0089[2:0])

Bias

blocks

Buffers

for SPI

signals

LMS7002M

CLKGEN_TOP

Analog signal lines

Signal input/output

RESET_N (XXXX)

IO control name (register adress)

EN_COARSEPLL_CGEN (0x0086[10])

PD_VCO _CGEN (0x0086[2])

PD_VCO _CGEN (0x0086[2])

PD_CP_CGEN (0x0086[6])

PD_FDIV_O_CGEN (0x0086[4])

Control signal lines

To: CLKADC (ADC)

To: CLKDAC (DAC)

REV_CLKDAC_CGEN (0x008A[14])

REV_CLKADC_CGEN (0x008A[13])

CLKH_OV_CLKL_CGEN<1:0> (0x0089[12-11])

EN_ADCCLKH_CLKGN (0x0086[11])

TST_CGEN<2:0> (0x0089[2:0])

TST_CGEN<2:0> (0x0089[2:0])

CMPLO_CTRL_CGEN (0x008B[14])

Loading...

Loading...