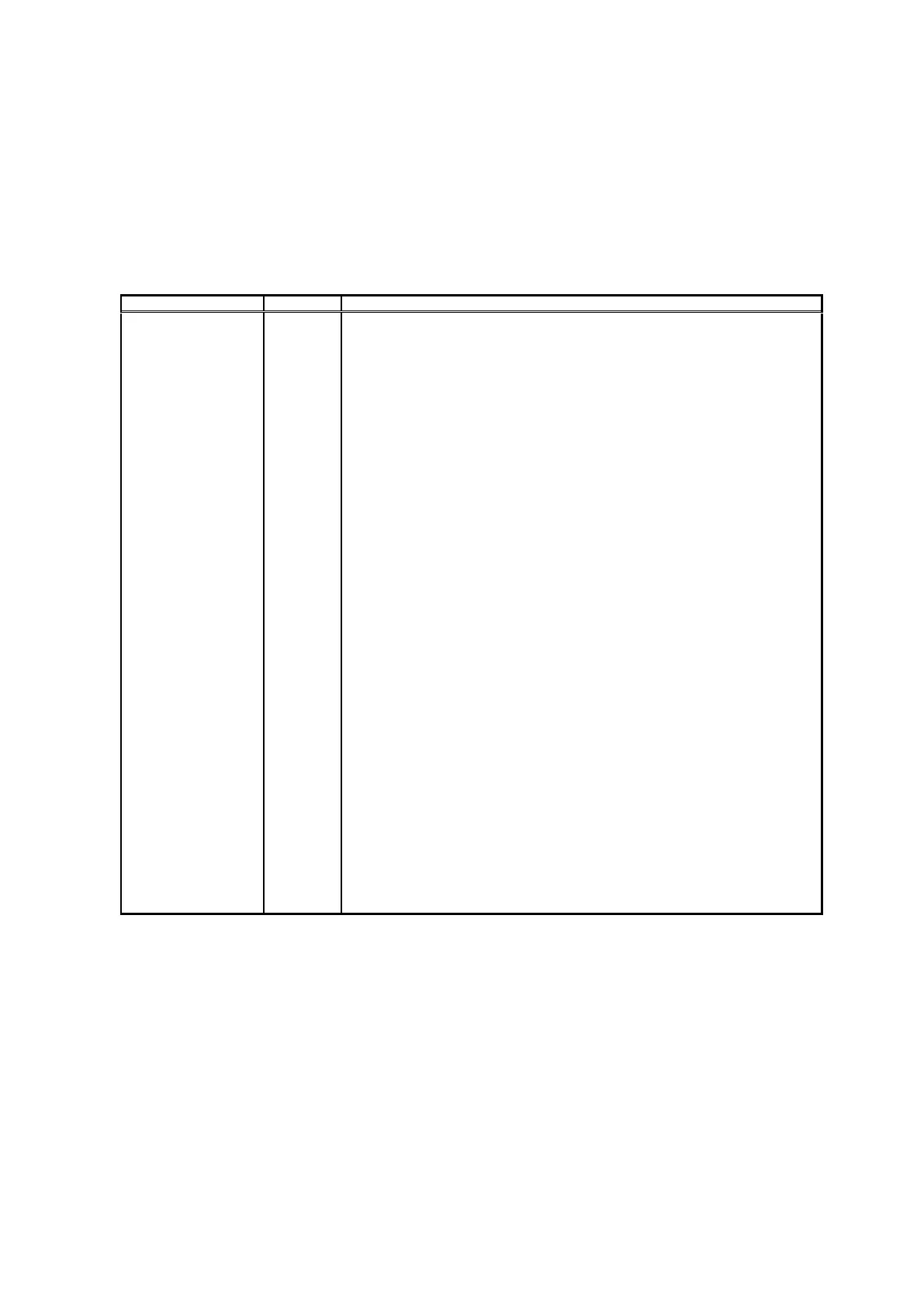

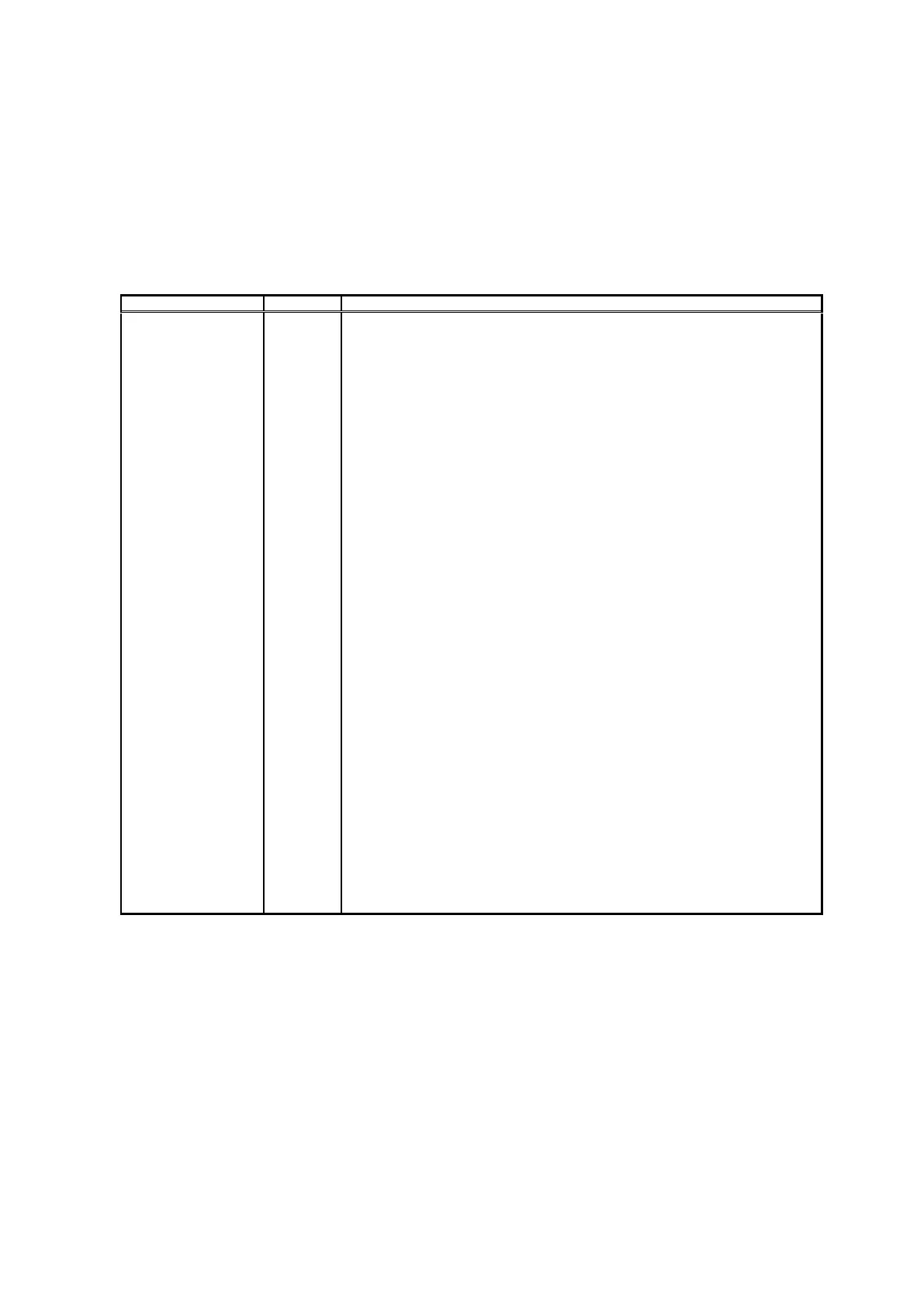

describe the control registers of the XBUF module.

Reserved

SLFB_XBUF_RX: Self biasing digital control.

1 – enable biasing the input's DC voltage level from the chip, the input

signal, IN, needs to be AC coupled to the chip

0 – disable the DC voltage level from the chip, the input signal, IN, needs

to be DC coupled to t o the chip (default)

SLFB_XBUF_TX: Self biasing digital control.

1 – enable biasing the input's DC voltage level from the chip, the input

signal, IN, needs to be AC coupled to the chip.

0 – disable the DC voltage level from the chip, the input signal, IN, needs

to be DC coupled to t o the chip. (default)

BYP_XBUF_RX: Shorts the Input 3.3V buffer in XBUF

The final 2 1.2V buffers are still active. The input in Bypass mode should be a 1.2V

full scale CMOS signal.

0 – Bypass not active (default)

1 – Bypass active

BYP_XBUF_TX: Shorts the Input 3.3V buffer in XBUF

The final 2 1.2V buffers are still active. The input in Bypass mode should be a 1.2V

full scale CMOS signal.

0 – Bypass not active (default)

1 – Bypass active

EN_OUT2_XBUF_TX: Enables the 2nd output of TX XBUF. This 2nd buffer goes to

XBUF_RX. This should be active when only 1 XBUF is to be used.

0 – TX XBUF 2nd output is active (default)

1 – TX XBUF 2nd output is disabled

EN_TBUFIN_XBUF_RX: Disables the input from the external XOSC and buffers the

2nd input signal (from TX XBUF 2nd output) to the RX. This should be active when

only 1 XBUF is to be used.

0 – RX XBUF input is coming from external XOSC (default)

1 – RX XBUF input is coming from TX

PD_XBUF_RX: Power down signal

0 – block active (default)

1 – block powered down

PD_XBUF_TX: Power down signal

0 – block active (default)

1 – block powered down

EN_G_XBUF: Enable control for all the XBUF power downs

0 – All XBUF modules powered down

1 – All XBUF modules controlled by individual power down registers

(default)

Default: 00000000 00000001

Loading...

Loading...