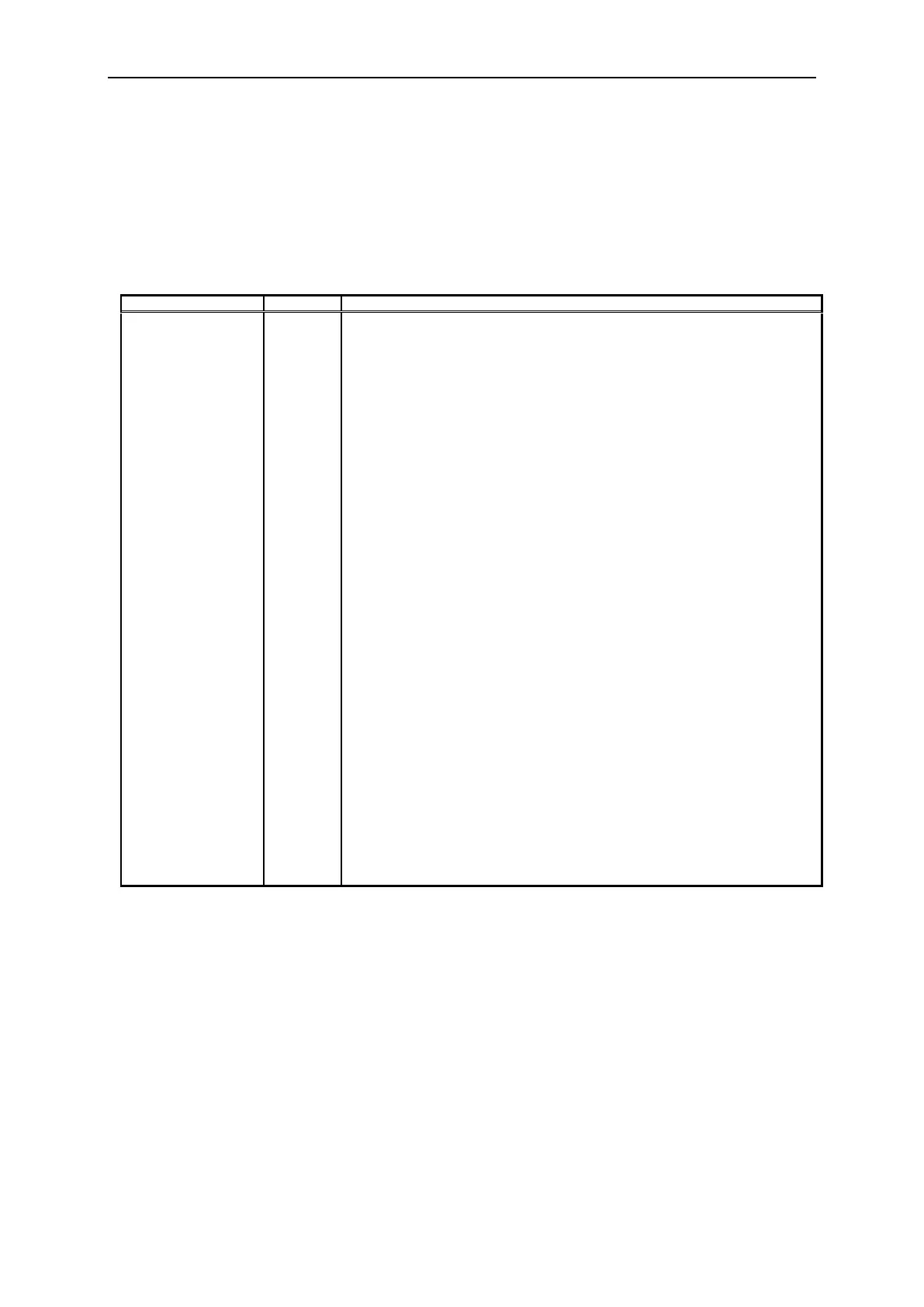

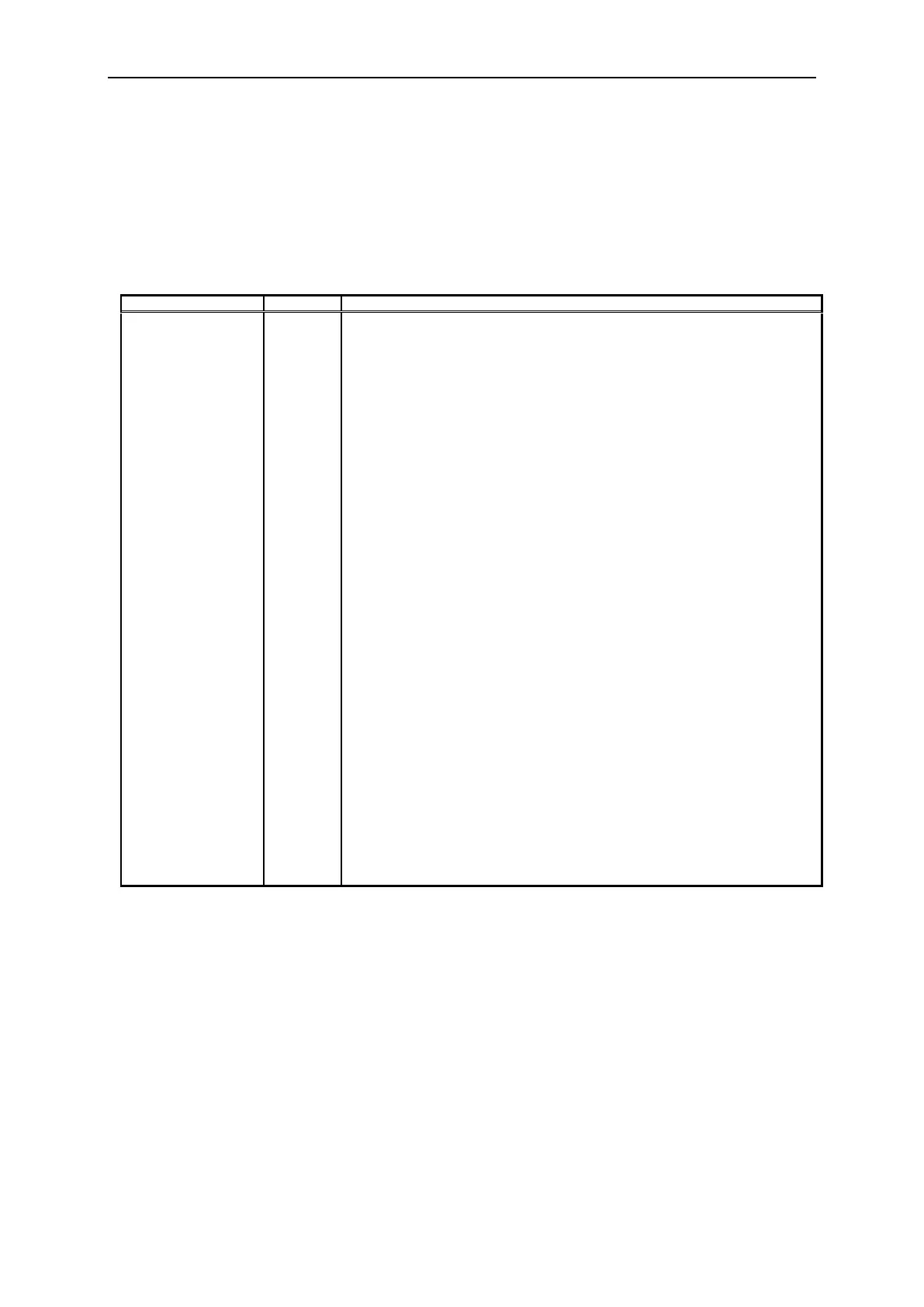

describe the control registers of the AFE module.

ISEL_DAC_AFE[2:0]: Controls the peak current of the DAC output current.

Default: 4

Iout_peak = 325uA+ISEL_DAC_AFE*75uA

Nominal = 625uA

MODE_INTERLEAVE_AFE: time interleaves the two ADCs into one ADC

0 – Two ADCs (default)

1 – Interleaved

MUX_AFE_1<1:0>: Controls the MUX at the input of the ADC channel 1

0 – MUX off, only PGA output is connected to ADC input (default)

1 – pdet_1 is connected to ADC channel 1. PGA should be powered down

2 – BIAS_TOP test outputs will be connected to ADC channel 1 input

(Please see MUX_BIAS_OUT<1:0>)

3 – RSSI 1 output will be connected to ADC 1 input

MUX_AFE_2<1:0>: Controls the MUX at the input of the ADC channel 2

0 – MUX off, only PGA output is connected to ADC input (default)

1 – pdet_2 is connected to ADC channel 2. PGA should be powered down

2 – RSSI 1 output will be connected to ADC 2 input

3 – RSSI 2 output will be connected to ADC 2 input

Reserved

PD_AFE: Power down control for the AFE current mirror in BIAS_TOP

0 – Active (default)

1 – powered down

PD_RX_AFE1: Power down control for the ADC of channel 1

0 – Active (default)

1 – powered down

PD_RX_AFE2: Power down control for the ADC of channel 2

0 – Active

1 – powered down (default)

PD_TX_AFE1: Power down control for the DAC of channel 1

0 – Active (default)

1 – powered down

PD_TX_AFE2: Power down control for the DAC of channel 2

0 – Active

1 – powered down (default)

EN_G_AFE: Enable control for all the AFE power downs

0 – All AFE modules powered down

1 – All AFE modules controlled by individual power down registers

(default)

Default: 10000000 00001011

Loading...

Loading...