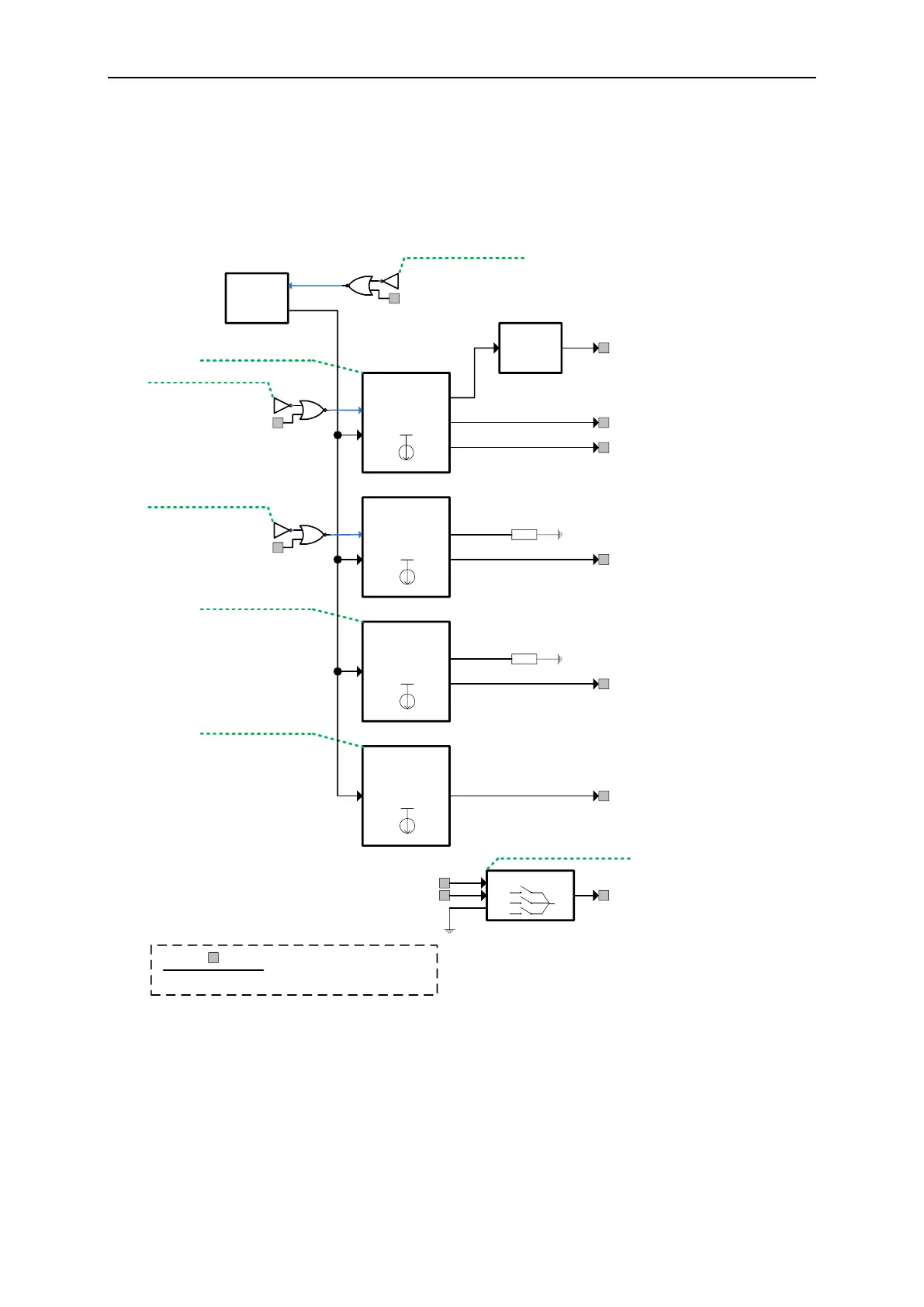

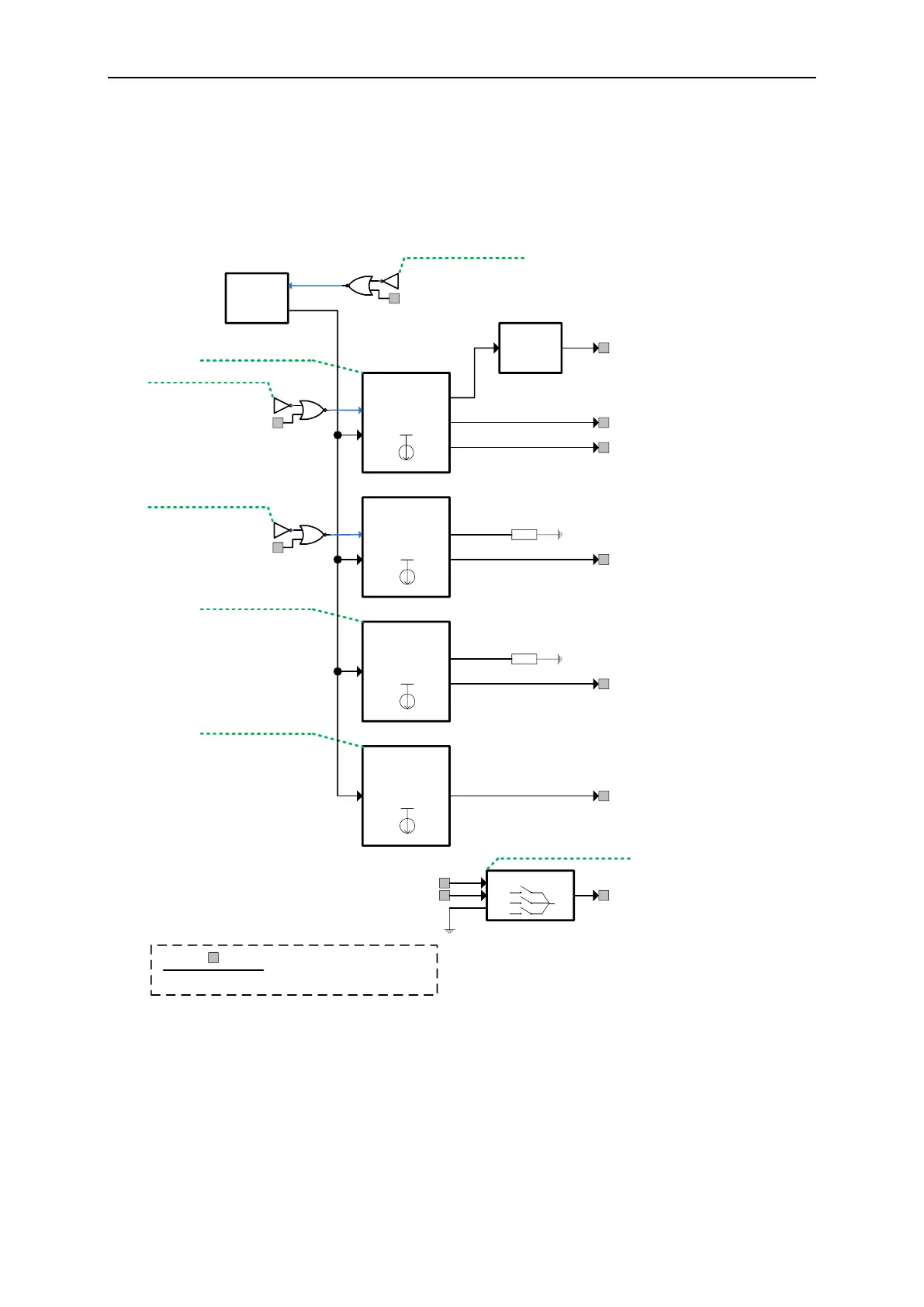

Current

Generator

F

Current

Generator

FRP

Current

Generator

PT

Current

Generator

PTRP

10k

AFE

bias

PD_F_BIAS (0x0084[3])

To: ip20f<47:1> (various blocks)

Bias

enable

block

MUX_BIAS_OUT (0x0084[12:11])

RP_CALIB_BIAS (0x0084[10:6])

PD_FRP_BIAS (0x0084[4])

PD_PTRP_BIAS (0x0084[2])

PD_BIAS_MASTER (0x0084[0])

RP_CALIB_BIAS (0x0084[10:6])

PD_PT_BIAS (0x0084[1])

To: vr_rext (PAD)

To: ip20frp<47:1> (various blocks)

To: ip20pt<50:1> (various blocks)

To: ip20ptrp<37:1> (various blocks)

10k

vr_cal_ref

vptat_600m

BIAS mux

From: vr_rext (PAD) and vr_cal_ref (internal)

From: vptat_600m (internal) and vr_cal_ref (internal) To: bias_top_adcin<1:0> (AFE MUX)

To: ADC and DAC (AFE)

Analog signal lines

Signal input/output

RESET_N (XXXX)

IO control name (register adress)

LMS7002M

BIAS

From: CORE_LDO_EN (PAD)

From: CORE_LDO_EN (PAD)

From: CORE_LDO_EN (PAD)

Loading...

Loading...