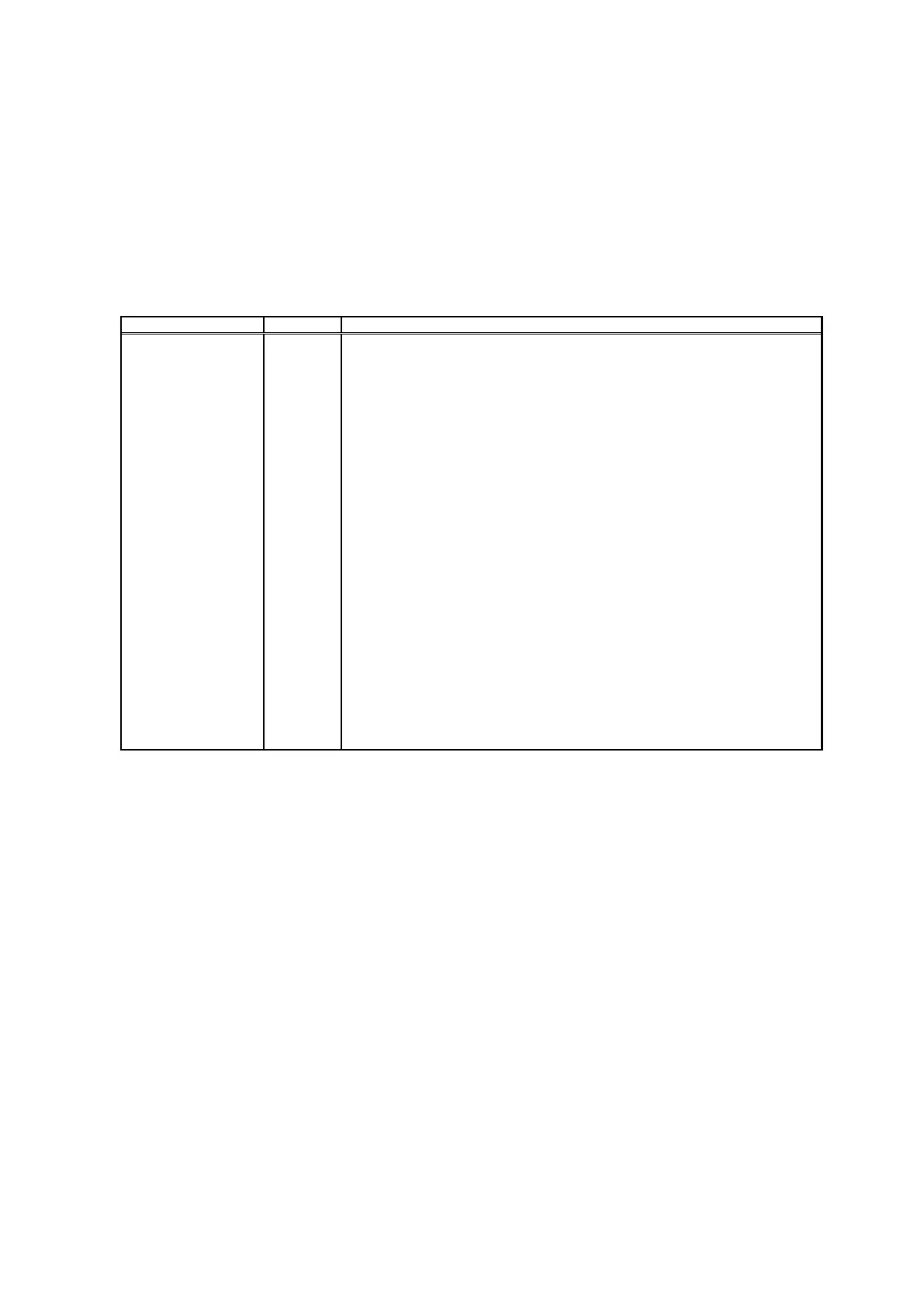

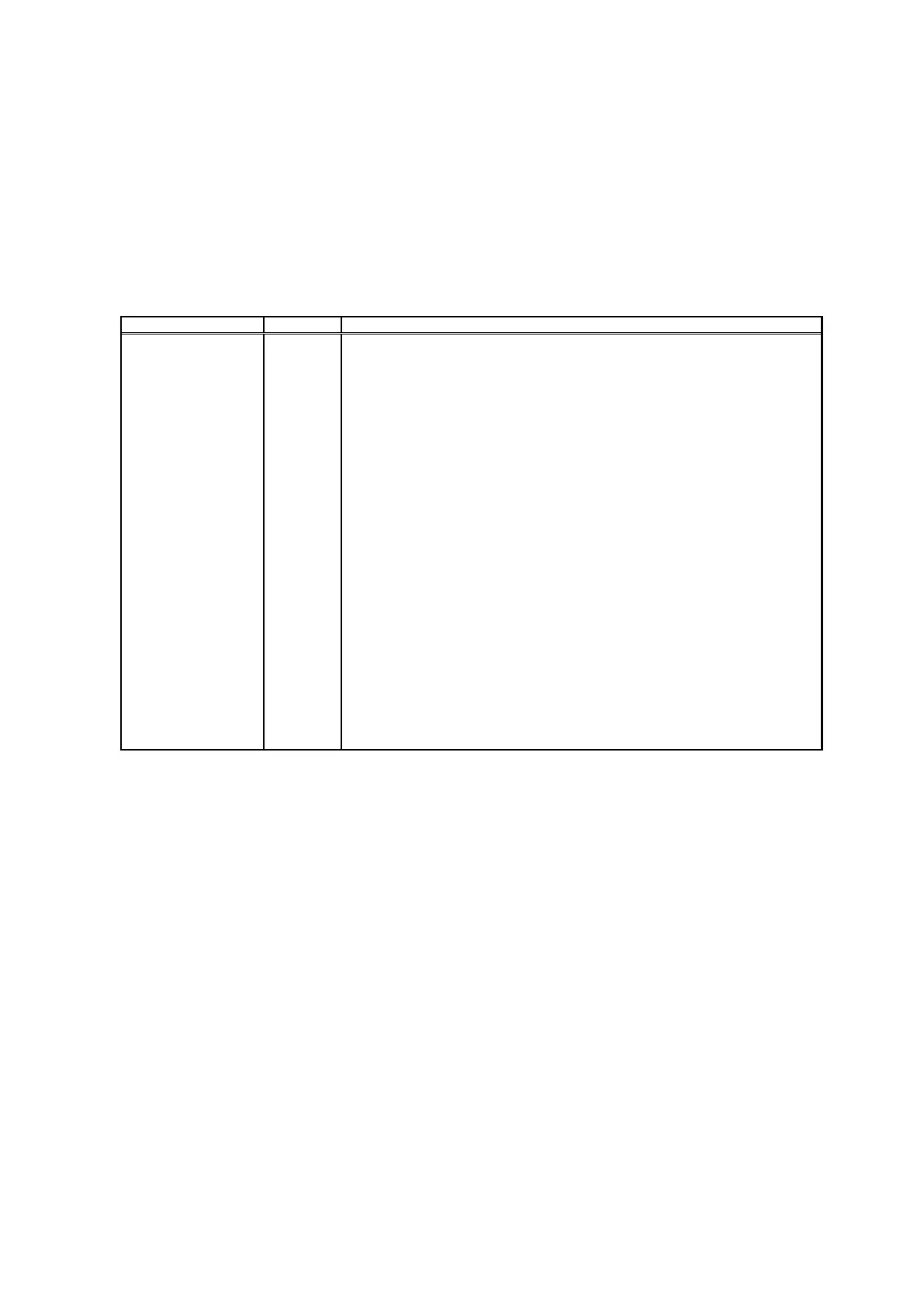

respectively. The tables in this chapter describes control registers of RFE1 and RFE2

modules.

CDC_I_RFE_(1,2)[3:0]: Trims the duty cycle in I channel. Default = 8;

CDC_Q_RFE_(1,2)[3:0]: Trims the duty cycle in Q channel. Default = 8;

PD_LNA_RFE_(1, 2): Power control signal for LNA_RFE

0 – block active

1 – block powered down (default)

PD_RLOOPB_1_RFE_(1, 2): Power control signal for RXFE loopback 1

0 – block active

1 – block powered down (default)

PD_RLOOPB_2_RFE_(1, 2): Power control signal for RXFE loopback 2

0 – block active

1 – block powered down (default)

PD_MXLOBUF_RFE_(1, 2): Power control signal for RXFE mixer lo buffer

0 – block active

1 – block powered down (default)

PD_QGEN_RFE_(1, 2): Power control signal for RXFE quadrature LO generator

0 – block active

1 – block powered down (default)

PD_RSSI_RFE_(1, 2): Power control signal for RXFE RSSI

0 – block active

1 – block powered down (default)

PD_TIA_RFE_(1, 2): Power control signal for RXFE TIA

0 – block active (default)

1 – block powered down

EN_G_RFE_(1, 2): Enable control for all the RFE_1 power downs

0 – All RFE_1 modules powered down

1 – All RFE_1 modules controlled by individual power down registers

(default)

Default: 10001000 11111101

Loading...

Loading...