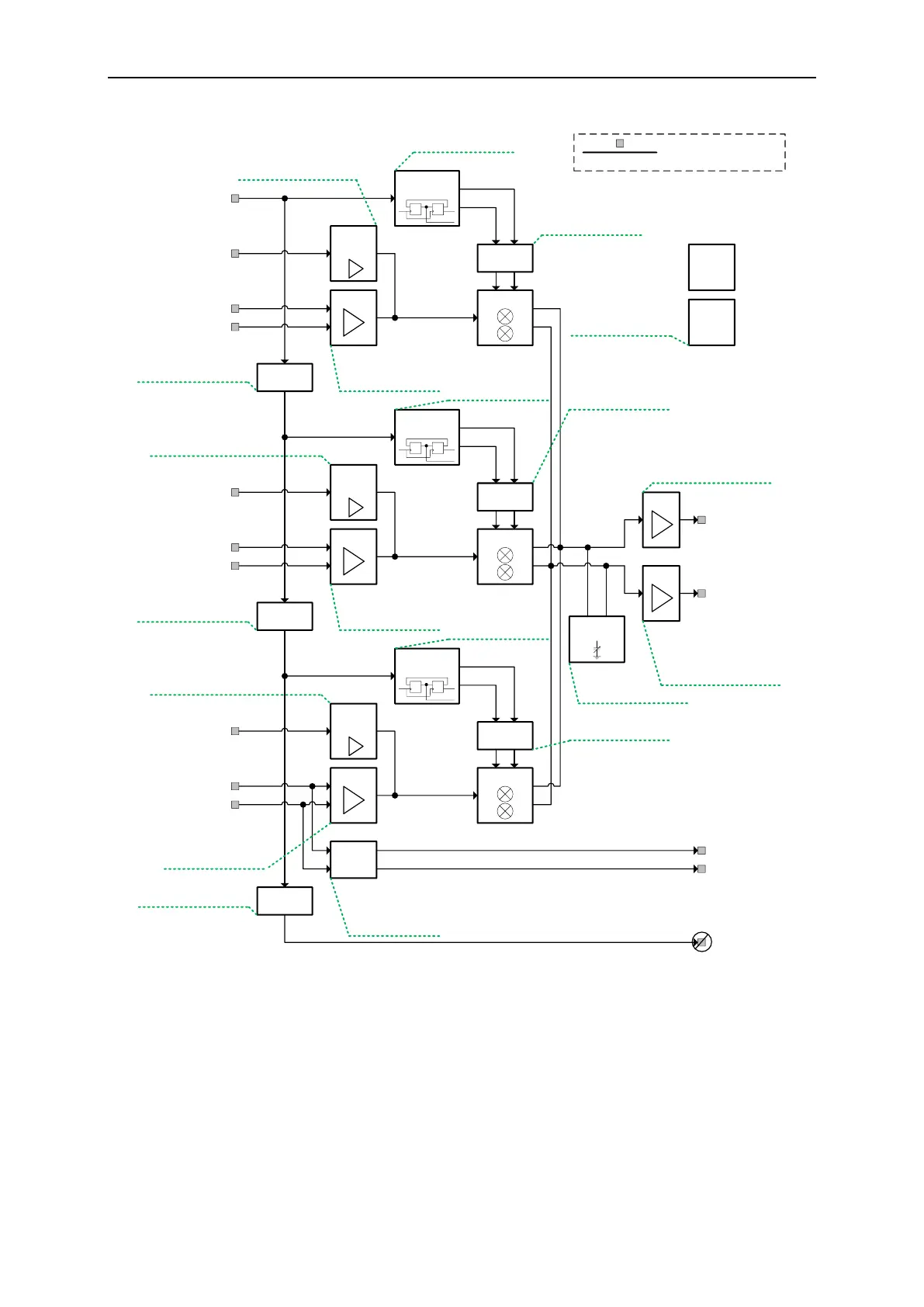

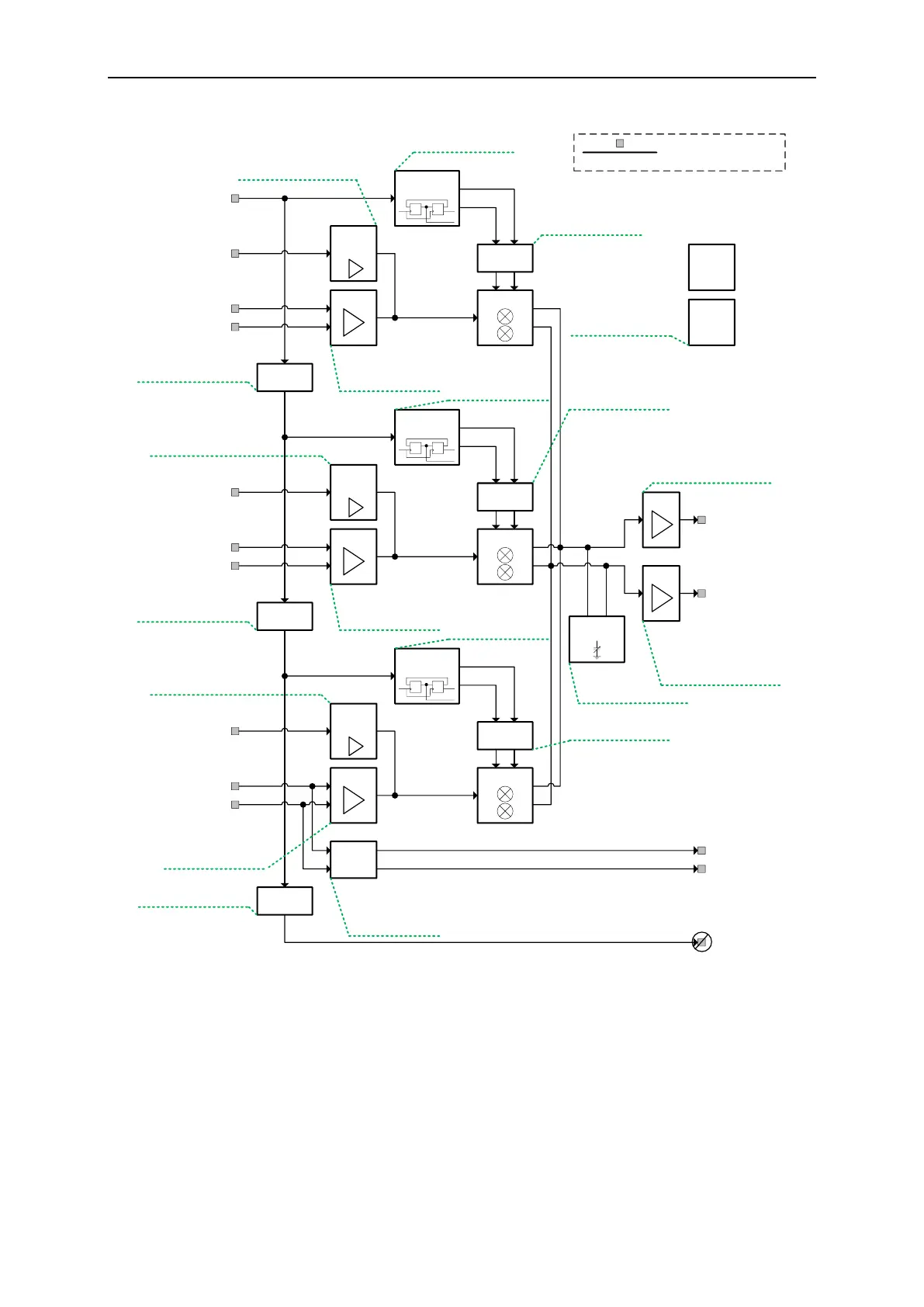

LMS7002M

RXFE_TOP 2

Bias

blocks

Buffers

for SPI

signals

TX mixer

output cap

TIA

LO I/Q

generator

RX RF

loopback

Buffer

Mixer

D

D

LO mixer

buffer

LO buff

LNA H

RSSI

LO I/Q

generator

RX RF

loopback

Buffer

Mixer

D

D

LO mixer

buffer

LO buff

LNA L

LO I/Q

generator

RX RF

loopback

Buffer

Mixer

D

D

LO mixer

buffer

LO buff

LNA W

TIA

To: rfeoi(p/n)_2 (RX BB)

To: rfeoq(p/n)_2 (RX BB)

To: out_rssi_rfe_2 (AFE mux,

or to PAD via tsdo<1> pin)

To: vrefout_rssi_rfe_2 (AFE mux,

or to PAD via tstao pin)

Frem: loopb2o(p/n)_trf2 (TX FE)

Frem: loopb1o(p/n)_trf2 (TX FE)

From: rfg(p/n)_h_RFE_2 (PAD)

From: rfs(p/n)_h_RFE_2 (PAD)

From: rfg(p/n)_l_RFE_2 (PAD)

From: rfs(p/n)_l_RFE_2 (PAD)

From: rfg(p/n)_w_RFE_2 (PAD)

From: rfs(p/n)_w_RFE_2 (PAD)

PD_QGEN_RFE_2 (0x010C[3])

PD_MXLOBUF_RFE_2 (0x010C[4])

PD_QGEN_RFE_2 (0x010C[3])

SEL_PATH_RFE_2 (0x010D[7:8])

SEL_PATH_RFE_2 (0x010D[7:8])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_LNA_RFE_2 (0x010C[7])

EN_INSHSW_H_RFE_2 (0x010D[5])

CGSIN_LNA_RFE_2 (0x0111[4:0])

G_LNA_RFE_2 (0x0113[9:6])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_RLOOPB_1_RFE_2 (0x010C[6])

PD_RLOOPB_2_RFE_2 (0x010C[5])

SEL_PATH_RFE_2 (0x010D[7:8])

EN_NEXTRX_RFE_2 (0x010D[0])

PD_RLOOPB_1_RFE_2 (0x010C[6])

SEL_PATH_RFE_2 (0x010D[7:8])

EN_NEXTRX_RFE_2 (0x010D[0])

EN_NEXTRX_RFE_2 (0x010D[0])

PD_RLOOPB_2_RFE_2 (0x010C[5])

EN_INSHSW_LB2_RFE_2 (0x010D[3])

G_RXLOOPB_RFE_2 (0x0113[5:2])

PD_MXLOBUF_RFE_2 (0x010C[4])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_MXLOBUF_RFE_2 (0x010C[4])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_QGEN_RFE_2 (0x010C[3])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_RLOOPB_1_RFE_2 (0x010C[6])

EN_INSHSW_LB1_RFE_2 (0x010D[4])

G_RXLOOPB_RFE_2 (0x0113[5:2])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_LNA_RFE_2 (0x010C[7])

CGSIN_LNA_RFE_2 (0x0111[4:0])

G_LNA_RFE_2 (0x0113[9:6])

EN_INSHSW_L_RFE_2 (0x010D[2])

SEL_PATH_RFE_2 (0x010D[7:8])

PD_LNA_RFE_2 (0x010C[7])

CGSIN_LNA_RFE_2 (0x0111[4:0])

G_LNA_RFE_2 (0x0113[9:6])

EN_INSHSW_W_RFE_2 (0x010D[1])

CAP_RXMXO_RFE_2 (0x0111[9:5])

Analog signal lines

Signal input/output

RESET_N (XXXX) IO control name (register adress)

DCOFFQ_RFE_2 (0x010E[6:0])

RFB_TIA_RFE_2 (0x0114[4:0])

PD

_

TIA

_

RFE

_

2

(

0

x

010

C

[

1

])

EN_DCOFF_RXFE_RFE_1(0x010D[6])

DCOFFI_RFE_2 (0x010E[13:7])

CCOMP_TIA_RFE_2 (0x0112[15:12])

CFB_TIA_RFE_2 (0x0112[11:0])

G_TIA_RFE_2 (0x0113[1:0])

RCOMP_TIA_RFE_2 (0x0114[8:5])

PD

_

TIA

_

RFE

_

2

(

0

x

010

C

[

1

])

EN_DCOFF_RXFE_RFE_1(0x010D[6])

CCOMP_TIA_RFE_2 (0x0112[15:12])

CFB_TIA_RFE_2 (0x0112[11:0])

G_TIA_RFE_2 (0x0113[1:0])

RCOMP_TIA_RFE_2 (0x0114[8:5])

RFB_TIA_RFE_2 (0x0114[4:0])

PD_LNA_RFE_2 (0x010C[7])

PD_RLOOPB_1_RFE_2 (0x010C[6])

PD_RLOOPB_2_RFE_2 (0x010C[5])

PD_MXLOBUF_RFE_2 (0x010C[4])

PD_TIA_RFE_2 (0x010C[1])

ICT_LOOPB_RFE_2 (0x010F[14:10])

ICT_TIAMAIN_RFE_2 (0x010F[9:5])

ICT_TIAOUT_RFE_2 (0x010F[4:0])

ICT_LNACMO_RFE_2 (0x0110[14:10])

ICT_LNA_RFE_2 (0x0110[9:5])

ICT_LODC_RFE_2 (0x0110[4:0])

Not routed

From: RLODIVO_OUT1 (RX RF 1)

CDC_I_RFE_2 (0x010C[15:12])

CDC_Q_RFE_2 (0x010C[11:8])

CDC_I_RFE_2 (0x010C[15:12])

CDC_Q_RFE_2 (0x010C[11:8])

CDC_I_RFE_2 (0x010C[15:12])

CDC_Q_RFE_2 (0x010C[11:8])

PD_RLOOPB_1_RFE_2 (0x010C[6])

EN_INSHSW_LB1_RFE_2 (0x010D[4])

G_RXLOOPB_RFE_2 (0x0113[5:2])

Frem: loopb1o(p/n)_trf2 (TX FE)

PD_RSSI_RFE_2 (0x010C[2])

ARSSI_CMPSTATUS_2 (0x0640[15])

ARSSI_RSEL_2 (0x0640[8:4])

ARSSI_HYSCMP_2 (0x0640[3:1])

ARSSI_DCO2_2 (0x0641[13:7])

ARSSI_DCO1_2 (0x0641[6:0])

ARSSI_PD_2 (0x0640[0])

Loading...

Loading...