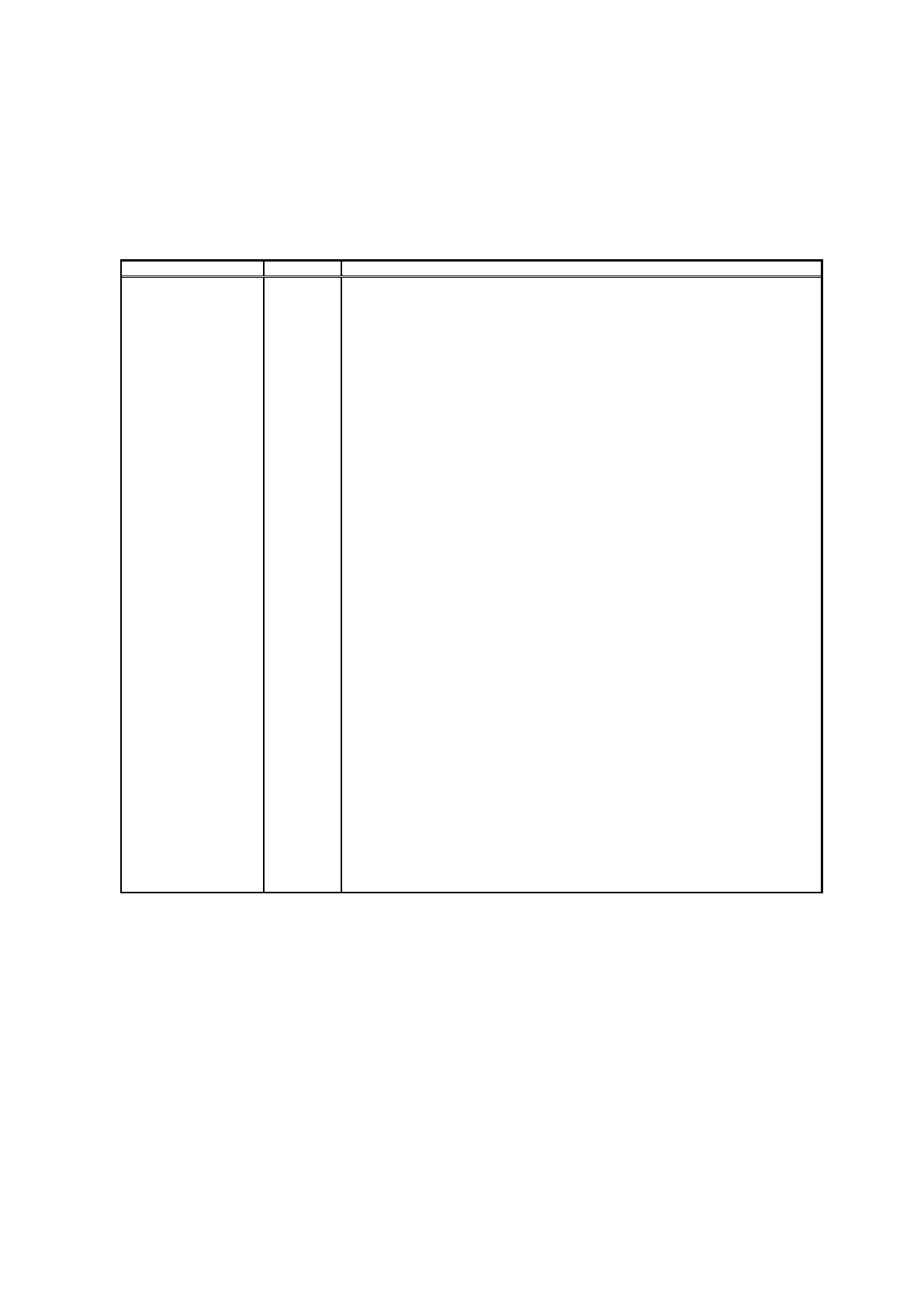

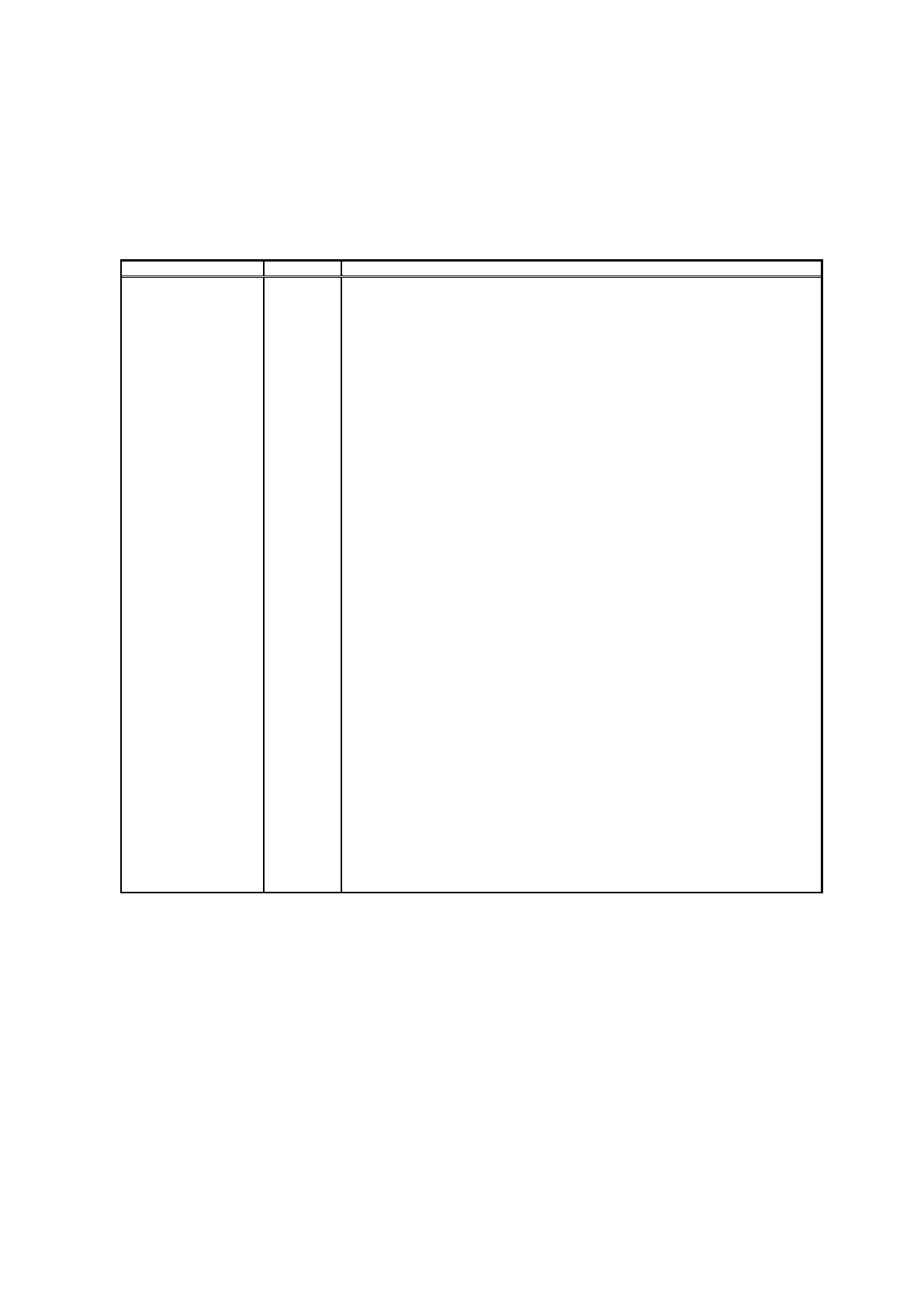

The tables in this chapter describe the control registers of CDS module.

CDS_MCLK2[1:0]: MCLK2 clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

CDS_MCLK1[1:0]: MCLK1 clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

Reserved

CDSN_TXBTSP: TX TSPB clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_TXATSP: TX TSPA clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_RXBTSP: RX TSPB clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_RXATSP: RX TSPA clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_TXBLML: TX LMLB clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_TXALML: TX LMLA clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_RXBLML: RX LMLB clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_RXALML: RX LMLA clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_MCLK2: MCLK2 clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

CDSN_MCLK1: MCLK1 clock inversion control.

0 – Clock is inverted

1 – Clock is not inverted (default)

Default: 00000011 11111111

Loading...

Loading...