60

2.19 EN_DIR Configuration Memory

The tables in this chapters describe the control registers of the EN_DIR module. Each

EN_DIR bit enables capability of direct control of PD (powerdown) and EN (enable) outputs.

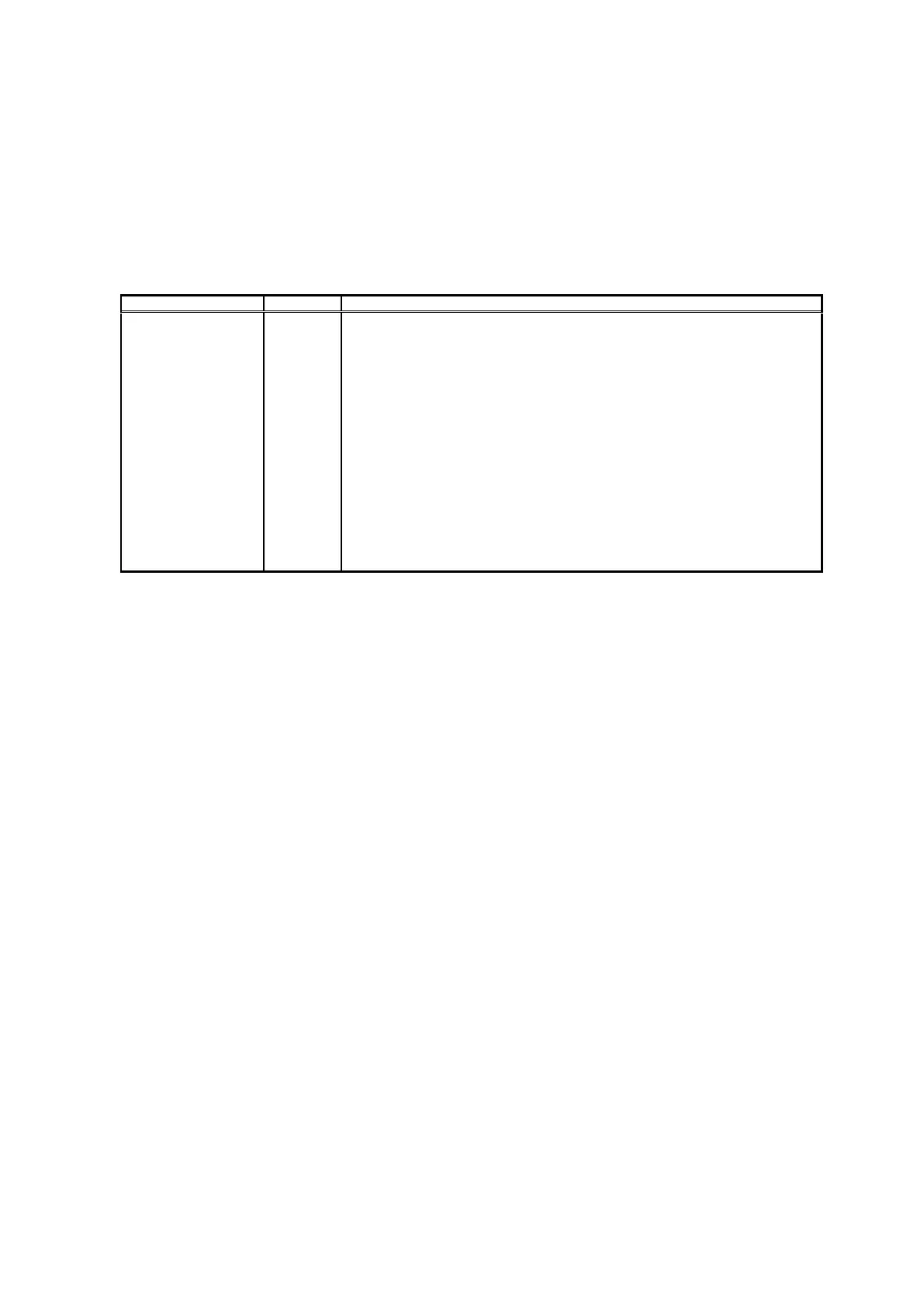

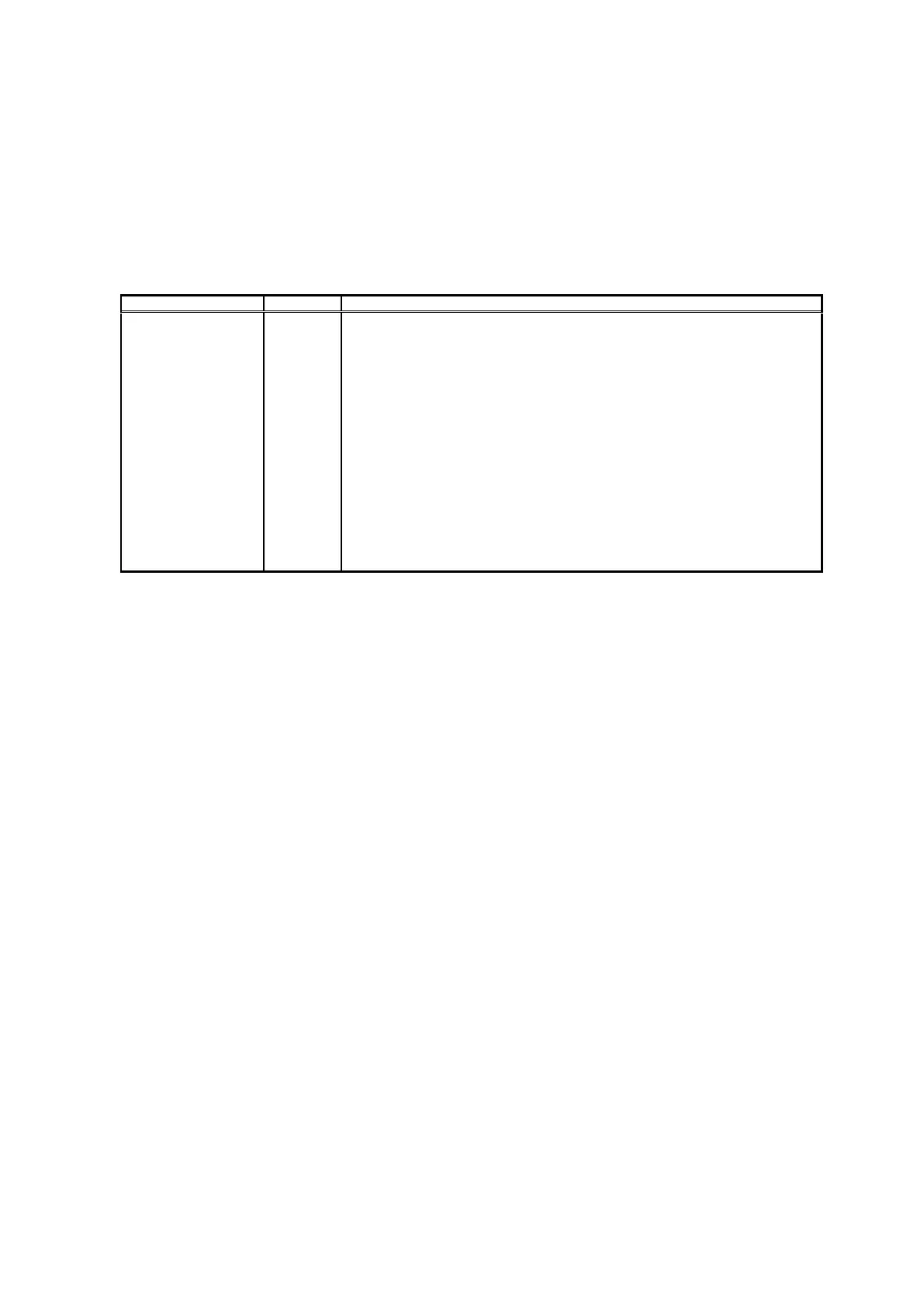

Table 20: EN_DIR configuration memory

TRX_GAIN_SRC: Alternative TRX gain source select. See section 2.12 for more

information.

0 – Gain control from separate registers (default)

1 – Gain control from combined registers

Reserved

EN_DIR_LDO: Enables direct control of PDs and ENs for LDO module.

0 – direct control disabled (default)

1 – direct control enabled

EN_DIR_CGEN: Enables direct control of PDs and ENs for CGEN module.

0 – direct control disabled (default)

1 – direct control enabled

EN_DIR_XBUF: Enables direct control of PDs and ENs for XBUF module.

0 – direct control disabled (default)

1 – direct control enabled

EN_DIR_AFE: Enables direct control of PDs and ENs for AFE module.

0 – direct control disabled (default)

1 – direct control enabled

Default: 00000000 00000000

For other modules (SX (R, T), RBB (1, 2), RFE (1, 2), TBB (1, 2), TRF (1, 2)) EN_DIR can

be controlled from register 0x0124.

Loading...

Loading...