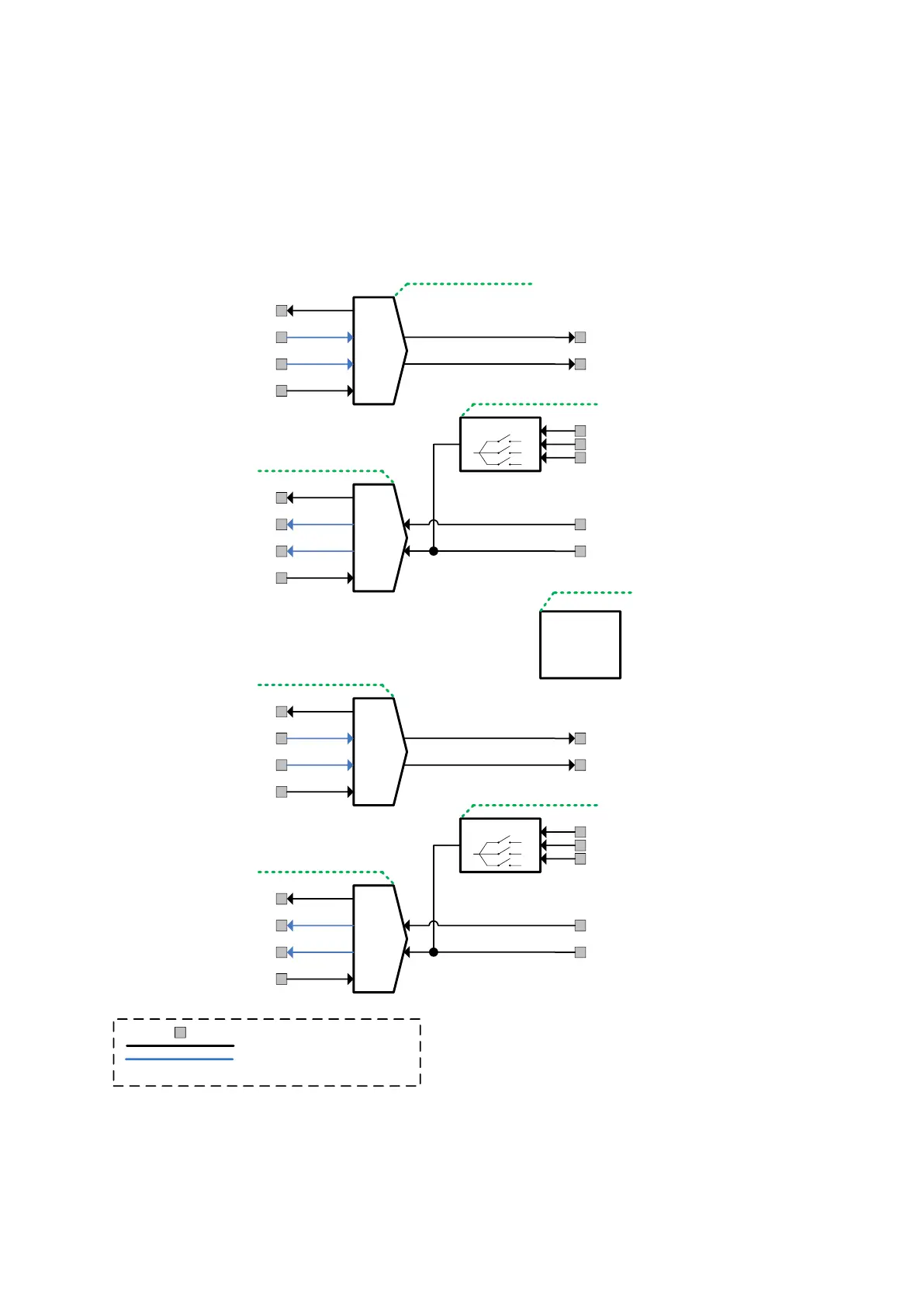

LMS7002M

AFE

AFE mux

DAC

core

ISEL_DAC_AFE (0x0082[15:13])

MUX_AFE_1 (0x0082[11:10])

MUX_AFE_2 (0x0082[9:8])

PD_AFE (0x0082[5])

PD_RX_AFE_1 (0x0082[4])

PD_RX_AFE_2 (0x0082[3])

PD_TX_AFE_1 (0x0082[2])

PD_TX_AFE_2 (0x0082[1])

From: DTXQ_AFE1<11:0> (TX TSP)

From: DTXI_AFE1<11:0> (TX TSP)

From: CLKDAC (CLKGEN)

To: CLKTX_OUT_A (CLK delay)

To: tbbii(p/n)_1 (TX BB)

To: tbbiq(p/n)_1 (TX BB)

ADC

core

From: rbboi(p/n)_1 (RX BB, external in)

From: rbboq(p/n)_1 (RX BB, external in)

From: pdeto(p/n)_1 (TX RF)

From: bias_top_adcin<1:0> (TOP BIAS)

From: out_rssi_rfe_1 and vrefout_rssi_rfe_1 (RX RF)

From: CLKADC (CLKGEN)

To: CLKRX_OUT_A (CLK delay)

To: DRXI_AFE1<11:0> (TX TSP)

To: DRXQ_AFE1<11:0> (TX TSP)

Top bias

block

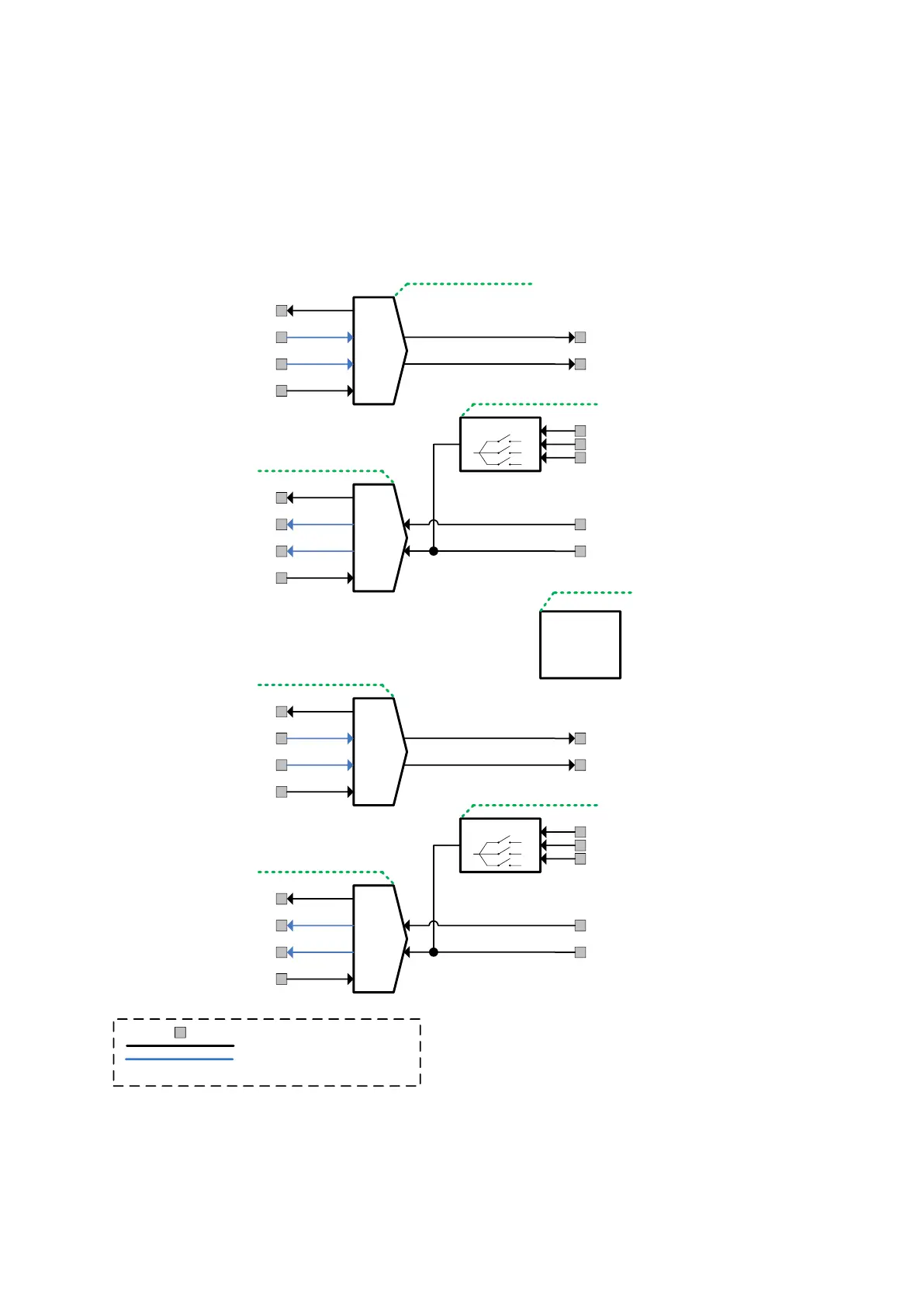

AFE mux

DAC

core

From: DTXQ_AFE2<11:0> (TX TSP)

From: DTXI_AFE2<11:0> (TX TSP)

From: CLKDAC (CLKGEN)

To: CLKTX_OUT_B (CLK delay)

To: tbbii(p/n)_2 (TX BB)

To: tbbiq(p/n)_2 (TX BB)

ADC

core

From: rbboi(p/n)_2 (RX BB, external in)

From: rbboq(p/n)_2 (RX BB, external in)

From: pdeto(p/n)_2 (TX RF)

From: out_rssi_rfe_2 and vrefout_rssi_rfe_2 (RX RF)

From: CLKADC (CLKGEN)

To: CLKRX_OUT_B (CLK delay)

To: DRXI_AFE2<11:0> (TX TSP)

To: DRXQ_AFE2<11:0> (TX TSP)

From: out_rssi_rfe_1 and vrefout_rssi_rfe_1 (RX RF)

ISEL_DAC_AFE (0x0082[15:13])

MODE_INTERLEAVE_AFE (0x0082[12])

MODE_INTERLEAVE_AFE (0x0082[12])

Analog signal lines

Signal input/output

RESET_N (XXXX)

IO control name (register adress)

Control signal lines

Loading...

Loading...