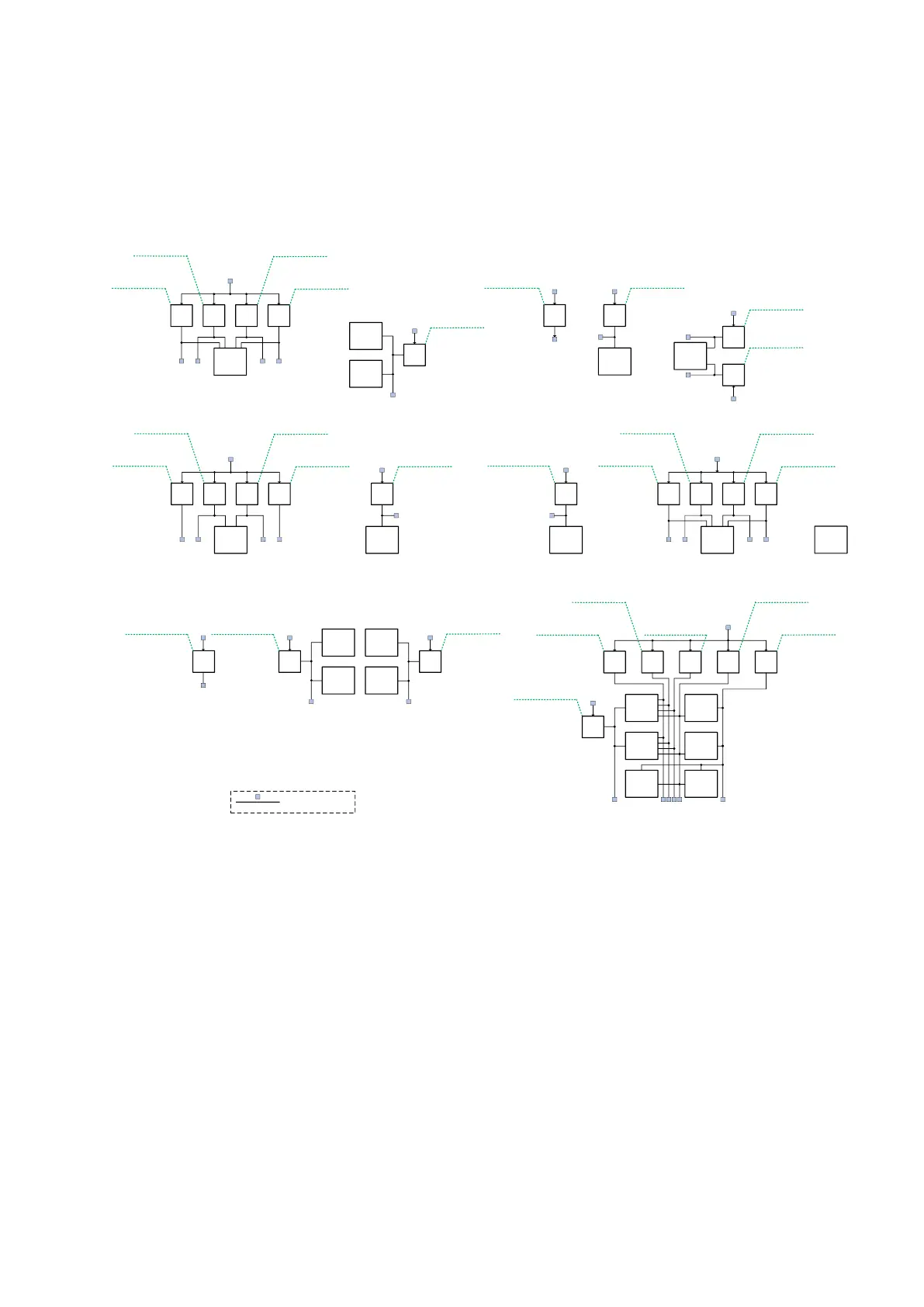

CLKGEN

Analog signal lines

Signal input/output

RESET_N (XXXX) IO control name (register adress)

BIAS

SX TX SX RX

TX FETX BB

RX FE RX BB

AFE

XBUF XBUF

TX FETX BB

RX FE RX BB

LDO

30m

LDO

240m

AFE

SPI

Digital

Padring

LDO

240m

VDD_TPAD_TRF

VDD18_LDO_TX

VDD18_LDO_TX

LDO

120m

VDD_TBB

VDD18_LDO_TX

VDD18_TXBUF

VDD12_TXBUF

VDD_CP_SXT

DVDD_SXT

VDD18_LDO_TX

LDO

120m

LDO

30m

LDO

30m

LDO

120m

LDO

30m

VDD18_RXBUF

VDD12_RXBUF

LDO

30m

VDD_CP_SXR

DVDD_SXR

LDO

120m

LDO

30m

LDO

30m

LDO

120m

VDD18_SXR

VDD_DIV_SXR

VDD12_VCO_SXR

DVDD_CGEN

VDD_CP_CGEN

LDO

30m

LDO

30m

LDO

30m

LDO

30m

VDD_DIV_CGEN

VDD14_VCO_CGEN

VDD18_VCO_CGEN

No LDO

LDO

120m

LDO

120m

LDO

30m

LDO

30m

LDO

30m

LDO

30m

VDD_MXLOBUF_RFE

VDD18_SXR

VDD18_LDO_RX

LDO

30m

VDD18_DIG

VDD12_DIG

VDD14_LNA_RFE

VDD12_LNA_RFE

VDD12_TIA_RFE

VDD14_RBB

LDO

30m

VDD14_TIA_RFE

VDDO_DIV_SXT

VDD12O_VCO_SXT

LDO

120m

VDD_AFE

VDD18_SXR

VDD_SPI_BUFF

DIGPRVDD1

(L33, R31)

DIGPRVDD1

(AA29, AE29)

DIGPRVDD2

(H32, T32)

DIGPRVDD2

(W33, AH30)

LDO

120m

VDDO_TLOBUF_TRF

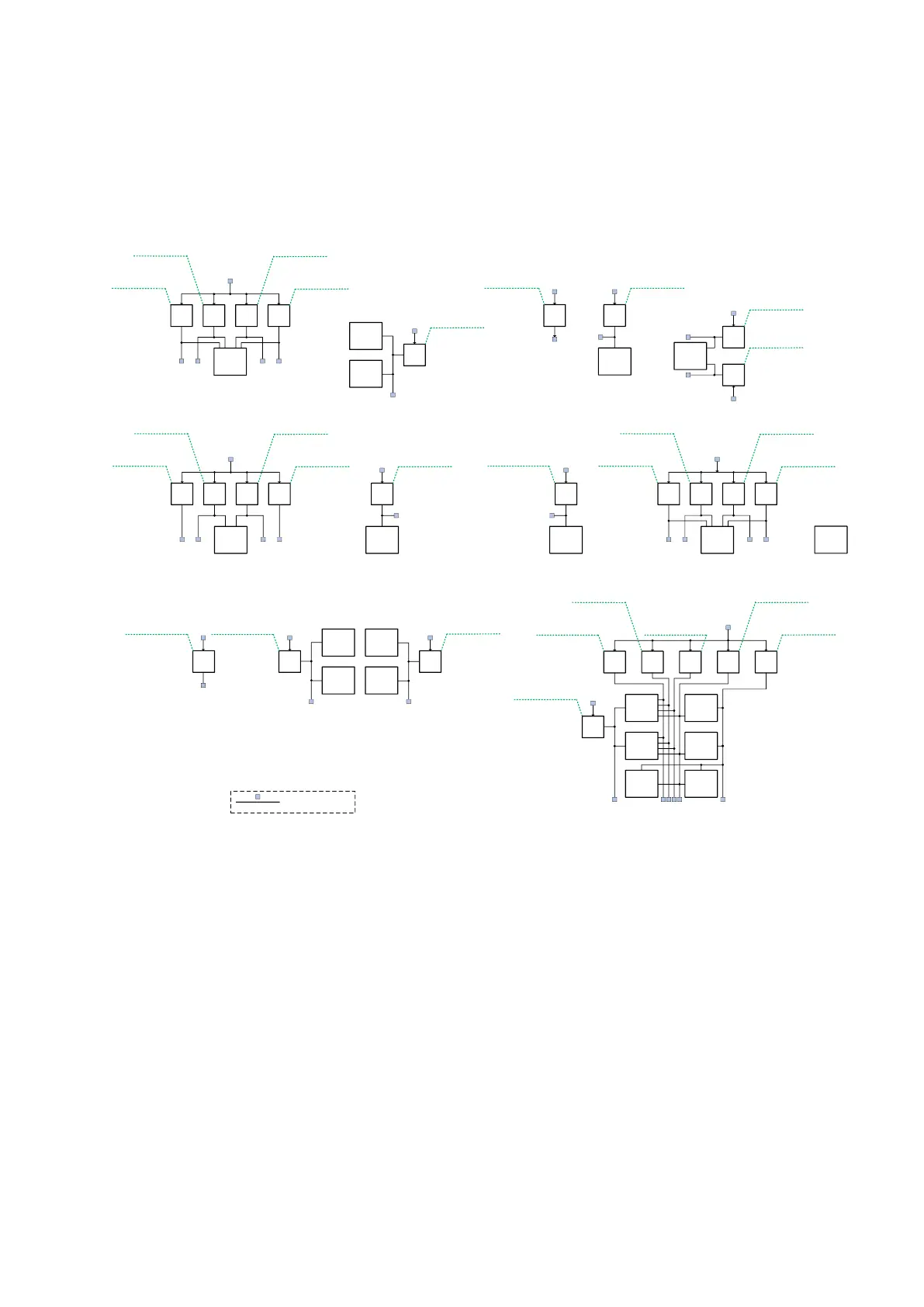

EN_LDO_DIVGN (0x0092[11])

EN_LOADIMP_LDO_DIVGN (0x0094[10])

BYP_LDO_DIVGN (0x0096[7])

SPDUP_LDO_DIVGN (0x0098[0])

RDIV_DIVGN<7:0> (0x00A1[7:0])

EN_LDO_DIGGN (0x0092[14])

EN_LOADIMP_LDO_DIGGN (0x0094[13])

BYP_LDO_DIGGN (0x0096[10])

SPDUP_LDO_DIGGN (0x0098[3])

RDIV_DIGGN<7:0> (0x00A2[15:8])

EN_LDO_VCOGN (0x0093[3])

EN_LOADIMP_LDO_VCOGN (0x0093[12])

BYP_LDO_VCOGN (0x0095[9])

SPDUP_LDO_VCOGN (0x0097[2])

RDIV_VCOGN<7:0> (0x009A[7:0])

EN_LDO_CPGN (0x0093[8])

EN_LOADIMP_LDO_CPGN (0x0095[1])

BYP_LDO_CPGN (0x0096[14])

SPDUP_LDO_CPGN (0x0098[7])

RDIV_CPGN<7:0> (0x00A4[15:8])

EN_LDO_DIG (0x0092[15])

EN_LOADIMP_LDO_DIG (0x0094[14])

BYP_LDO_DIG (0x0096[11])

SPDUP_LDO_DIG (0x0098[4])

RDIV_DIG<7:0> (0x00A3[7:0])

EN_LDO_DIVSXT (0x0092[9])

EN_LOADIMP_LDO_DIVSXT (0x0094[8])

BYP_LDO_DIVSXT (0x0096[5])

SPDUP_LDO_DIVSXT (0x0097[14])

RDIV_DIVSXT<7:0> (0x00A0[7:0])

EN_LDO_CPSXT (0x0093[0])

EN_LOADIMP_LDO_CPSXT (0x0094[15])

BYP_LDO_CPSXT (0x0096[12])

SPDUP_LDO_CPSXT (0x0098[5])

RDIV_CPSXT<7:0> (0x00A3[15:8])

EN_LDO_VCOSXT (0x0093[1])

EN_LOADIMP_LDO_VCOSXT (0x0093[10])

BYP_LDO_VCOSXT (0x0095[7])

SPDUP_LDO_VCOSXT (0x0097[0])

RDIV_VCOSXT<7:0> (0x0099[7:0])

EN_LDO_DIGSXT (0x0092[12])

EN_LOADIMP_LDO_DIGSXT (0x0094[11])

BYP_LDO_DIGSXT (0x0096[8])

SPDUP_LDO_DIGSXT (0x0098[1])

RDIV_DIGSXT<7:0> (0x00A1[15:8])

EN_LDO_TXBUF (0x0093[4])

EN_LOADIMP_LDO_TXBUF (0x0093[13])

BYP_LDO_TXBUF (0x0095[10])

SPDUP_LDO_TXBUF (0x0097[3])

RDIV_TXBUF<7:0> (0x009A[15:8])

EN_LDO_RXBUF (0x0092[4])

EN_LOADIMP_LDO_RXBUF (0x0094[3])

BYP_LDO_RXBUF (0x0096[0])

SPDUP_LDO_RXBUF (0x0097[9])

RDIV_RXBUF<7:0> (0x009D[15:8])

EN_LDO_DIVSXR (0x0092[10])

EN_LOADIMP_LDO_DIVSXR (0x0094[9])

BYP_LDO_DIVSXR (0x0096[6])

SPDUP_LDO_DIVSXR (0x0097[15])

RDIV_DIVSXR<7:0> (0x00A0[15:8])

EN_LDO_CPSXR (0x0093[7])

EN_LOADIMP_LDO_CPSXR (0x0095[0])

BYP_LDO_CPSXR (0x0096[13])

SPDUP_LDO_CPSXR (0x0098[6])

RDIV_CPSXR<7:0> (0x00A4[7:0])

EN_LDO_VCOSXR (0x0093[2])

EN_LOADIMP_LDO_VCOSXR (0x0093[11])

BYP_LDO_VCOSXR (0x0095[8])

SPDUP_LDO_VCOSXR (0x0097[1])

RDIV_VCOSXR<7:0> (0x0099[15:8])

EN_LDO_DIGSXR (0x0092[13])

EN_LOADIMP_LDO_DIGSXR (0x0094[12])

BYP_LDO_DIGSXR (0x0096[9])

SPDUP_LDO_DIGSXR (0x0098[2])

RDIV_DIGSXR<7:0> (0x00A2[7:0])

EN_LDO_TLOB (0x0093[6])

EN_LOADIMP_LDO_TLOB (0x0093[15])

BYP_LDO_TLOB (0x0095[12])

SPDUP_LDO_TLOB (0x0097[5])

RDIV_TLOB<7:0> (0x009B[15:8])

EN_LDO_TBB (0x0092[3])

EN_LOADIMP_LDO_TBB (0x0094[2])

BYP_LDO_TBB (0x0095[15])

SPDUP_LDO_TBB (0x0097[8])

RDIV_TBB<7:0> (0x009D[7:0])

EN_LDO_TPAD (0x0093[5])

EN_LOADIMP_LDO_TPAD (0x0093[14])

BYP_LDO_TPAD (0x0095[11])

SPDUP_LDO_TPAD (0x0097[4])

RDIV_TPAD<7:0> (0x009B[7:0])

EN_LDO_LNA14 (0x0092[7])

EN_LOADIMP_LDO_LNA14 (0x0094[6])

BYP_LDO_LNA14 (0x0096[3])

SPDUP_LDO_LNA14 (0x0097[12])

RDIV_LNA14<7:0> (0x009F[7:0])

EN_LDO_LNA12 (0x0092[8])

EN_LOADIMP_LDO_LNA12 (0x0094[7])

BYP_LDO_LNA12 (0x0096[4])

SPDUP_LDO_LNA12 (0x0097[13])

RDIV_LNA12<7:0> (0x009F[15:8])

EN_LDO_RBB (0x0092[5])

EN_LOADIMP_LDO_RBB (0x0094[4])

BYP_LDO_RBB (0x0096[1])

SPDUP_LDO_RBB (0x0097[10])

RDIV_RBB<7:0> (0x009E[7:0])

EN_LDO_TIA12 (0x0092[2])

EN_LOADIMP_LDO_TIA12 (0x0094[1])

BYP_LDO_TIA12 (0x0095[14])

SPDUP_LDO_TIA12 (0x0097[7])

RDIV_TIA12<7:0> (0x009C[15:8])

EN_LDO_TIA14 (0x0092[1])

EN_LOADIMP_LDO_TIA14 (0x0094[0])

BYP_LDO_TIA14 (0x0095[13])

SPDUP_LDO_TIA14 (0x0097[6])

RDIV_TIA14<7:0> (0x009C[7:0])

AFE PGA

PADIN

AFE PGA

PADIN

EN_LDO_AFE (0x0093[9])

EN_LOADIMP_LDO_AFE (0x0095[2])

BYP_LDO_AFE (0x0096[15])

SPDUP_LDO_AFE (0x0098[8])

RDIV_AFE<7:0> (0x00A5[7:0])

PD_LDO_SPIBUF (0x00A6[3])

EN_LOADIMP_LDO_SPIBUF (0x00A6[6])

BYP_LDO_SPIBUF (0x00A6[9])

SPDUP_LDO_SPIBUF (0x00A6[12])

RDIV_SPIBUF<7:0> (0x00A5[15:8]) PD_LDO_DIGIp2 (0x00A6[2])

EN_LOADIMP_LDO_DIGIp2 (0x00A6[5])

BYP_LDO_DIGIp2 (0x00A6[8])

SPDUP_LDO_DIGIp2 (0x00A6[11])

RDIV_DIGIp2<7:0> (0x00A7[15:8])

PD_LDO_DIGIp1 (0x00A6[1])

EN_LOADIMP_LDO_DIGIp1 (0x00A6[4])

BYP_LDO_DIGIp1 (0x00A6[7])

SPDUP_LDO_DIGIp1 (0x00A6[10])

RDIV_DIGIp1<7:0> (0x00A7[7:0])

EN_LDO_MXRFE (0x0092[6])

EN_LOADIMP_LDO_MXRFE (0x0094[5])

BYP_LDO_MXRFE (0x0096[2])

SPDUP_LDO_MXRFE (0x0097[11])

RDIV_MXRFE<7:0> (0x009E[15:8])

VDD18_DIG

ISINK_SPIBUFF<2:0> (0x00A6[15:13])

Loading...

Loading...