32

2.9 RBB(1, 2) Configuration Memory

The block diagrams of RBB1 and RBB2 modules are shown in Figure 7 Figure 8 respectively.

The tables in this chapter describe the control registers of RBB1 and RBB2 modules.

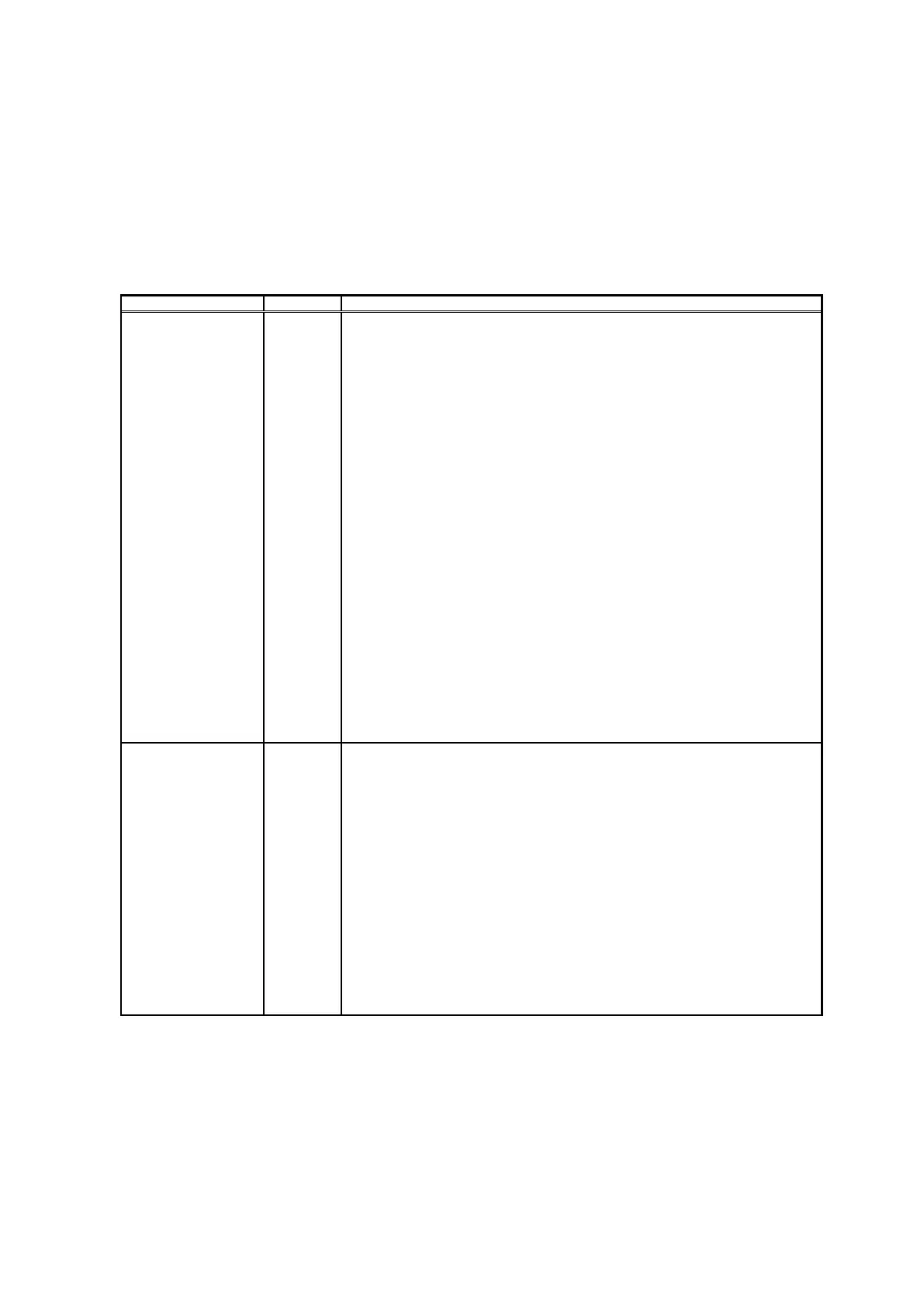

Table 10: RBB(1, 2) configuration memory

EN_LB_LPFH_RBB_(1, 2): This is the loopback enable signal that is enabled when

high band LPFH_RBB is selected for the loopback path that connects the loopb_lpfi

inputs to the virtual ground of the LPFH_RBB block.

1 – enabled

0 – disabled (default)

Note: Only one of EN_LB_LPFH_RBB/EN_LB_LPFL_RBB can be

enabled concurrently.

EN_LB_LPFL_RBB_(1, 2): This is the loopback enable signal that is enabled when

the high-band low pass filter LPFL_RBB is selected for the loopback path that

connects the loopb_lpf inputs to the virtual ground of the LPFL_RBB block.

1 – enabled

0 – disabled (default)

Note: Only one of EN_LB_LPFH_RBB/EN_LB_LPFL_RBB can be

enabled concurrently.

Reserved

PD_LPFH_RBB_(1, 2): Power down of the LPFH block.

0 – active

1 – powered down (default)

PD_LPFL_RBB_(1, 2): Power down of the LPFL block.

0 – active (default)

1 – powered down

PD_PGA_RBB_(1, 2): Power down of the PGA block.

0 – active (default)

1 – powered down

EN_G_RBB_(1, 2): Enable control for all the RBB_1 power downs

0 – All RBB modules powered down

1 – All RBB modules controlled by individual power down registers

(default)

Default: 00000000 00001001

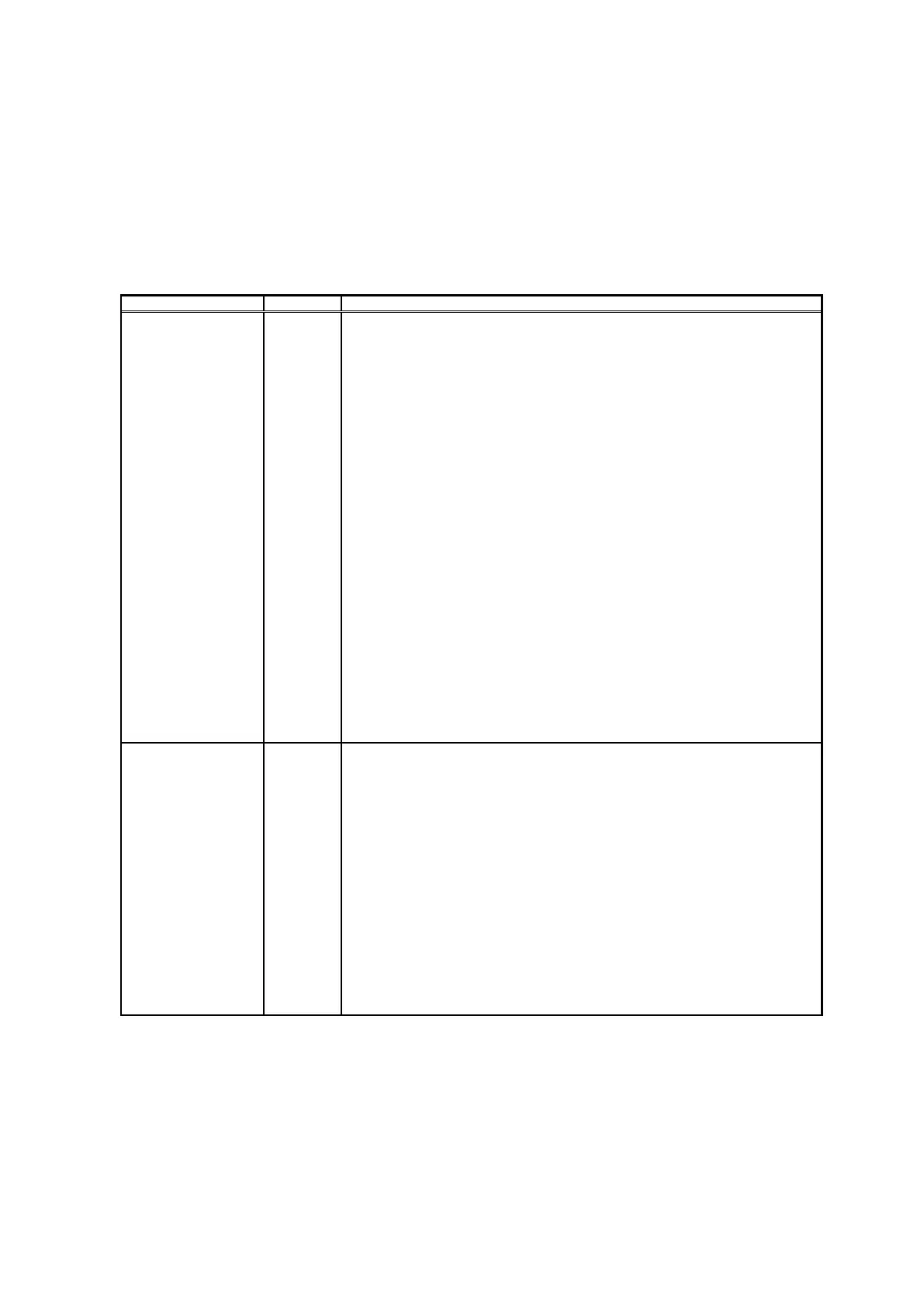

R_CTL_LPF_RBB_(1, 2)[4:0]: Controls the absolute value of the resistance of the

RC time constant of the RBB_LPF blocks (both Low and High).

This value is corrected during the calibration process. Default: 16

RCC_CTL_LPFH_RBB_(1, 2)[2:0]: Controls the stability passive compensation of

the LPFH_RBB operational amplifier. Default: 1

1 – when rxMode is 37MHz,

4 – when rxMode 66MHz,

7 – when rxMode 108MHz

C_CTL_LPFH_RBB_(1, 2)[7:0]: Controls the capacitance value of the RC time

constant of RBB_LPFH and it varies with the respective rxMode from 37MHz to

108MHz.

Its value is equal to (120*108M/rxMode)*ccor-cfrH; where: rxMode is the receiver

mode of operation 37MHz up to 108MHz, ccor is determined by calibration and cfrL

is valued at 56.

This control signal can be determined by lookup tables generated during the

calibration phase. Default: 128

Default: 10000001 00000000

Loading...

Loading...