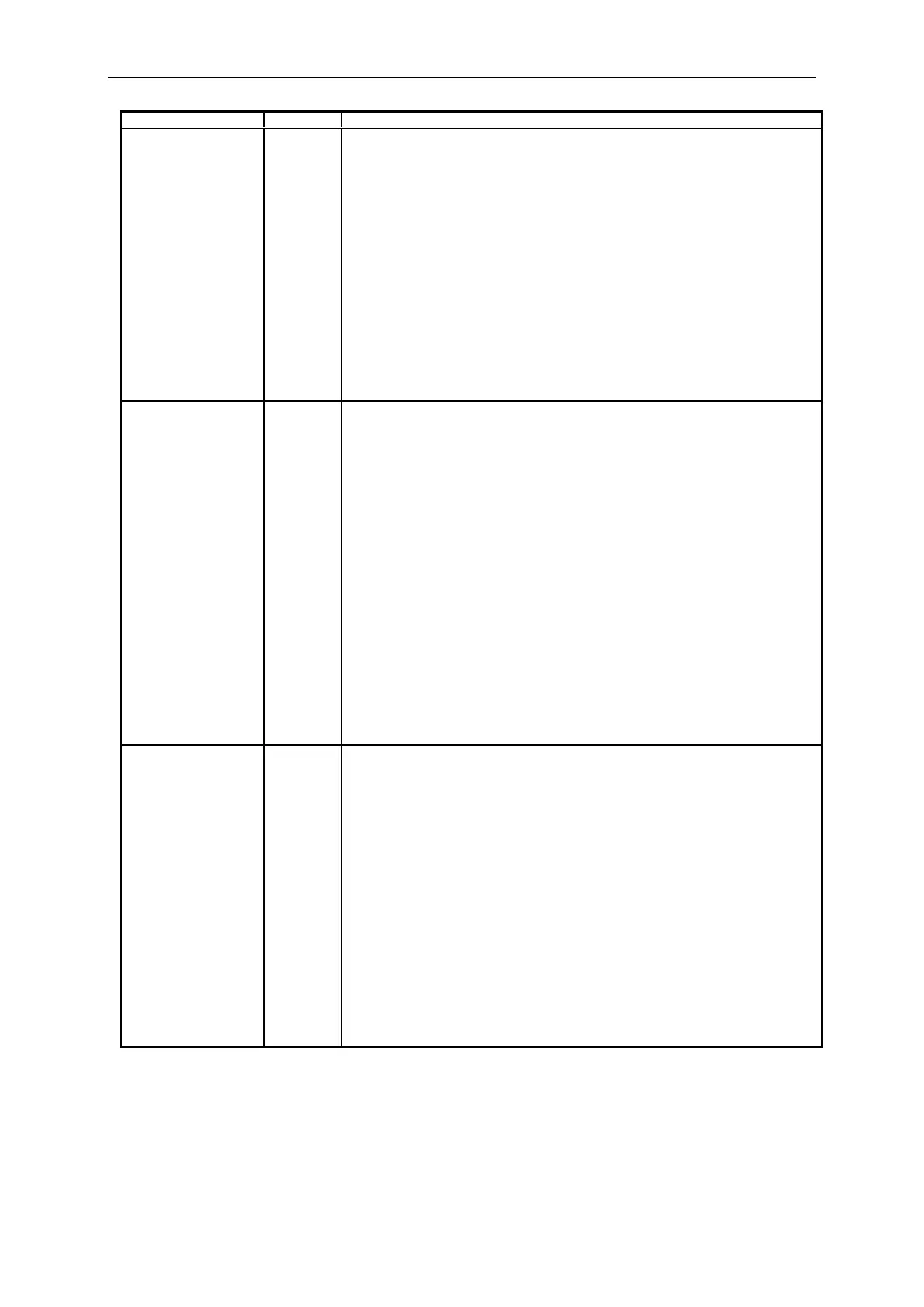

33

Reserved

RCC_CTL_LPFL_RBB_(1, 2)[2:0]: Controls the stability passive compensation of

the LPFL_RBB operational amplifier.

0 – when rxMode is 1.4MHz,

1 – when 3MHz

2 – when 5MHz

3 – when 10MHz

4 – when 15MHz

5 – when 20MHz (default)

C_CTL_LPFL_RBB_(1, 2)[10:0]: Controls the capacitance value of the RC time

constant of RBB_LPFL and it varies with the respective rxMode from 1.4MHz to

20MHz.

Its value is equal to (120*20M/rxMode)*ccor-cfrL ; where: rxMode is the receiver

mode of operation from 1.4MHz up to 20MHz, ccor is determined by calibration and

cfrL is valued at 100.

This control signal can be determined by lookup tables generated during the

calibration phase. Default: 12

Default: 00101000 00001100

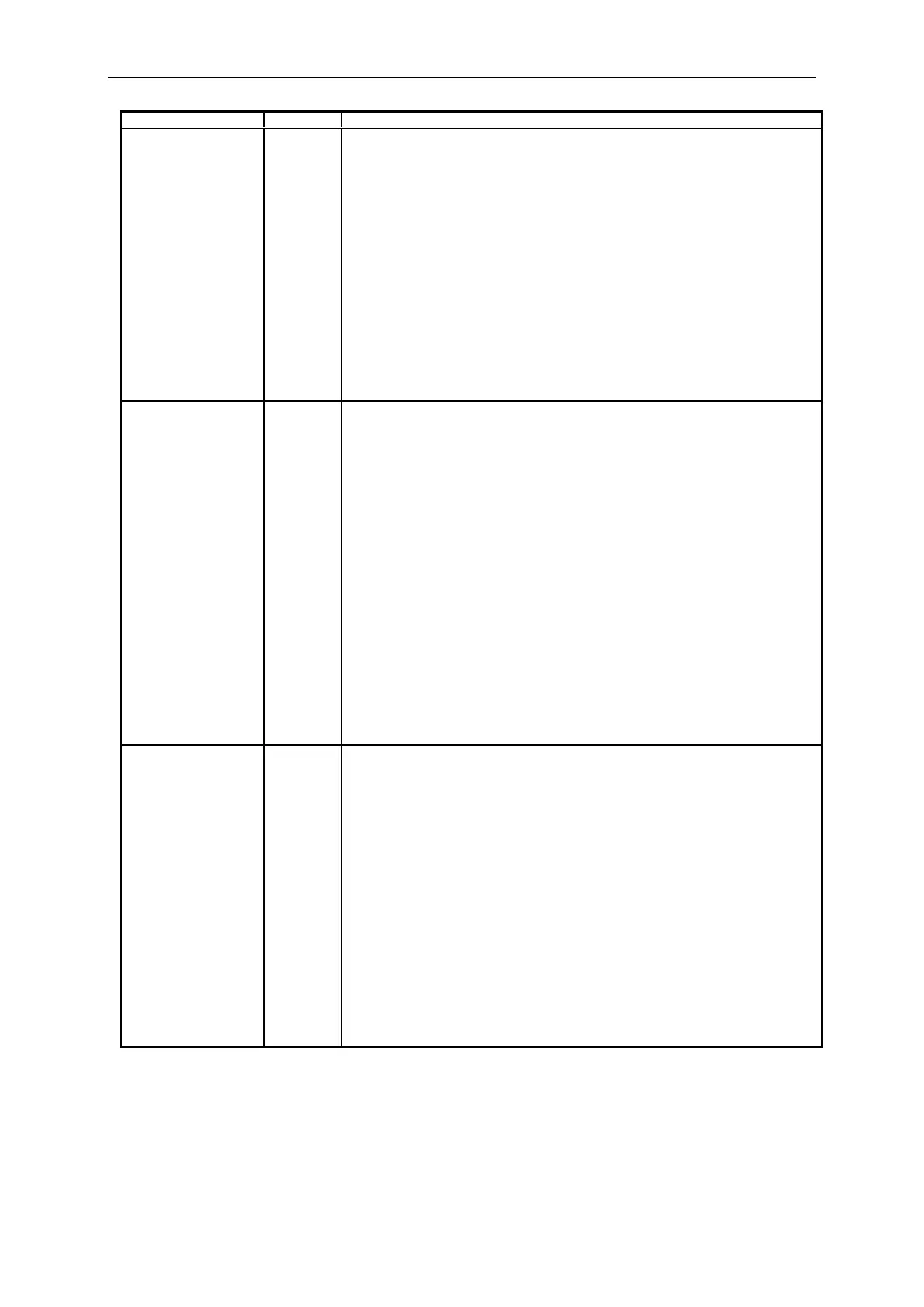

15-13

12 – 10

9 – 5

4 – 0

INPUT_CTL_PGA_RBB_(1, 2)[2:0]: There are a total of four different differential

inputs to the PGA. Only one of them is active at a time.

0 – when LPFL input is selected (rxMode [=20MHz); The output of the

LPFL_RBB block is selected as input. (default)

1 – when LPFH input is selected (rxMode ] 20MHz); The output of the

LPFH_RBB is selected as input.

2 – when bypassing the LPF blocks; The input signal to either RBB_LPFH

or RBB_LPFL is bypassed and connected directly to the PGA bypass

input.

3 – when connecting loopb_tx (the loop back from TBB) to the input of the

PGA.

4 – when loopb_pkd (Loop back path from the peak detector) is selected.

Reserved

ICT_LPF_IN_RBB_(1, 2)[4:0]: Controls the reference bias current of the input stage

of the operational amplifier used in RBB_LPF blocks (Low or High). Must increase

up to 24 when a strong close blocker is detected to maintain the linearity

performance. Default: 12

ICT_LPF_OUT_RBB_(1, 2)[4:0]: Controls the reference bias current of the output

stage of the operational amplifier used in RBB_LPF blocks (low or High). Must

increase up to 24 when a strong close blocker is detected to maintain the linearity

performance. Default: 12

Default: 00000001 10001100

OSW_PGA_RBB_(1, 2): There are two instances of the PGA circuit in the design.

The output of the RBB_LPF blocks are connected the input of these PGA blocks

(common). The output of one of them is connected to two pads pgaoutn and

pgaoutp and the output of the other PGA is connected directly to the ADC input.

0 – the PGA connected to the ADC is selected; (default)

1 – the PGA connected to the output pads is selected instead.

ICT_PGA_OUT_RBB_(1, 2)[4:0]: Controls the output stage reference bias current of

the operational amplifier used in the PGA circuit.

Must increase up to 12 when a strong close blocker is detected or when operating at

the high band frequencies to maintain the linearity performance. Default: 6

ICT_PGA_IN_RBB_(1, 2)[4:0]: Controls the input stage reference bias current of the

operational amplifier used in the PGA circuit.

Must increase up to 12 when a strong close blocker is detected or when operating at

the high band frequencies to maintain the linearity performance. Default: 6

G_PGA_RBB_(1, 2)[4:0]: This is the gain of the PGA. The gain is adaptively set to

maintain signal swing of 0.6Vpkd at the output of the PGA. The value of the gain is:

Gain(dB) = -12+G_PGA_RBB. Default: 11

Default: 00011000 11001011

Loading...

Loading...