91

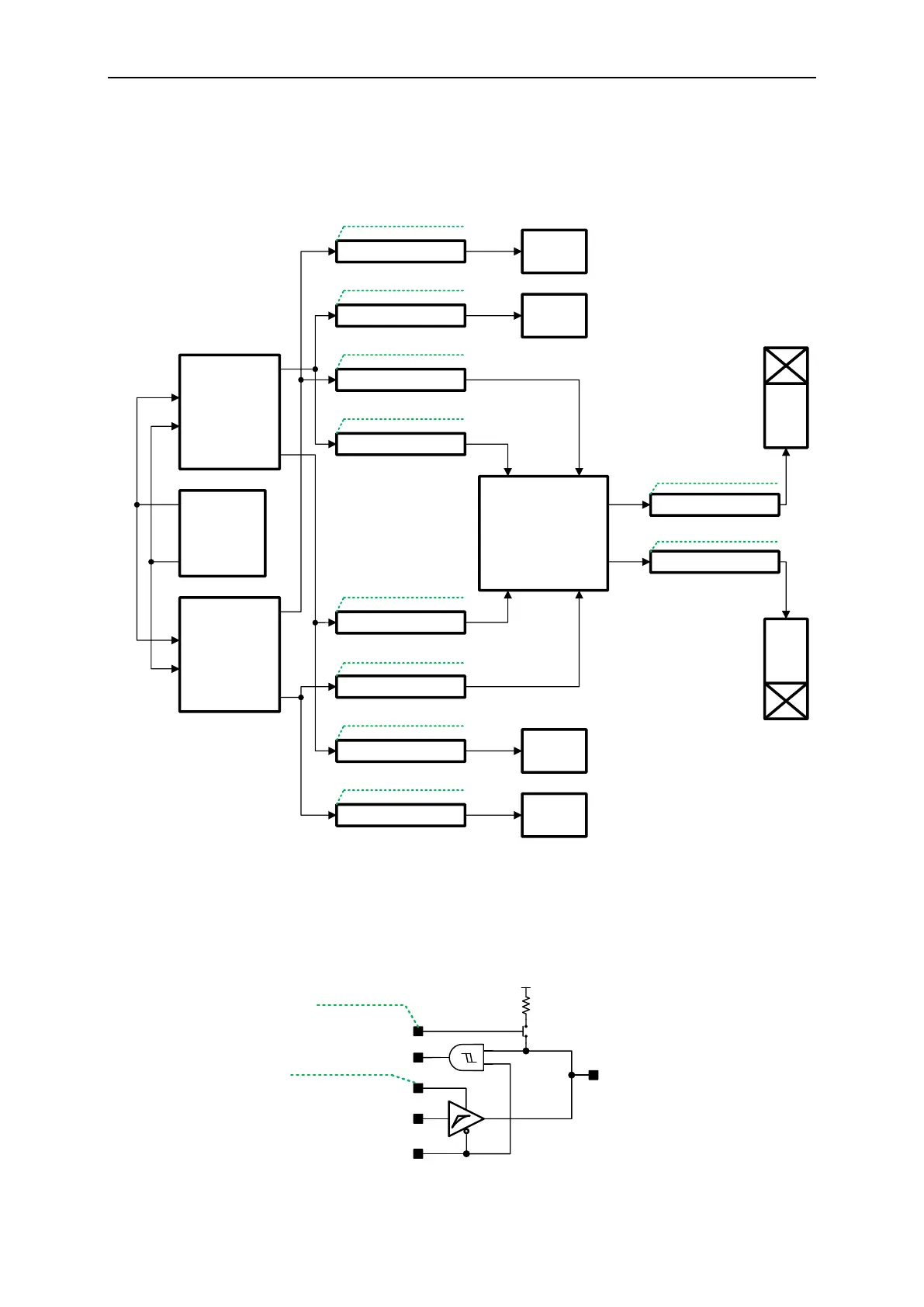

A2.11 CDS Control Diagram

LML Module

rxtspclkBrxtspclkA

txtspclkBtxtspclkA

mclk1

mclk2

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

Clock Delay Module

TxTSP A

TxTSP B

RxTSP B

RxTSP A

PAD MCLK2

PAD MCLK1

CGEN

CLKADC_OUT

CLKDAC_OUT

CKRX_IN

CKRX_OUT

CKTX_OUT

CKTX_IN

IAFE1

CKRX_IN

CKRX_OUT

CKTX_OUT

CKTX_IN

IAFE2

CDS_TXALML (0x00AF[5:4])

CDSN_TXALML (0x00AD[4])

CDS_TXBTSP (0x00AF[15:14])

CDSN_TXBTSP (0x00AD[9])

CDS_TXATSP (0x00AF[13:12])

CDSN_TXATSP (0x00AD[8])

CDS_TXBLML (0x00AF[7:6])

CDSN_TXBLML (0x00AD[5])

CDS_RXALML (0x00AF[1:0])

CDSN_RXALML (0x00AD[2])

CDS_RXBLML (0x00AF[3:2])

CDSN_RXBLML (0x00AD[3])

CDS_RXATSP (0x00AF[9:8])

CDSN_RXATSP (0x00AD[6])

CDS_RXBTSP (0x00AF[11:10])

CDSN_RXBTSP (0x00AD[7])

CDS_MCLK1 (0x00AF[13:12])

CDSN_MCLK1 (0x00AD[0])

CDS_MCLK2 (0x00AF[15:14])

CDSN_MCLK2 (0x00AD[1])

Figure 20 CDS control structure

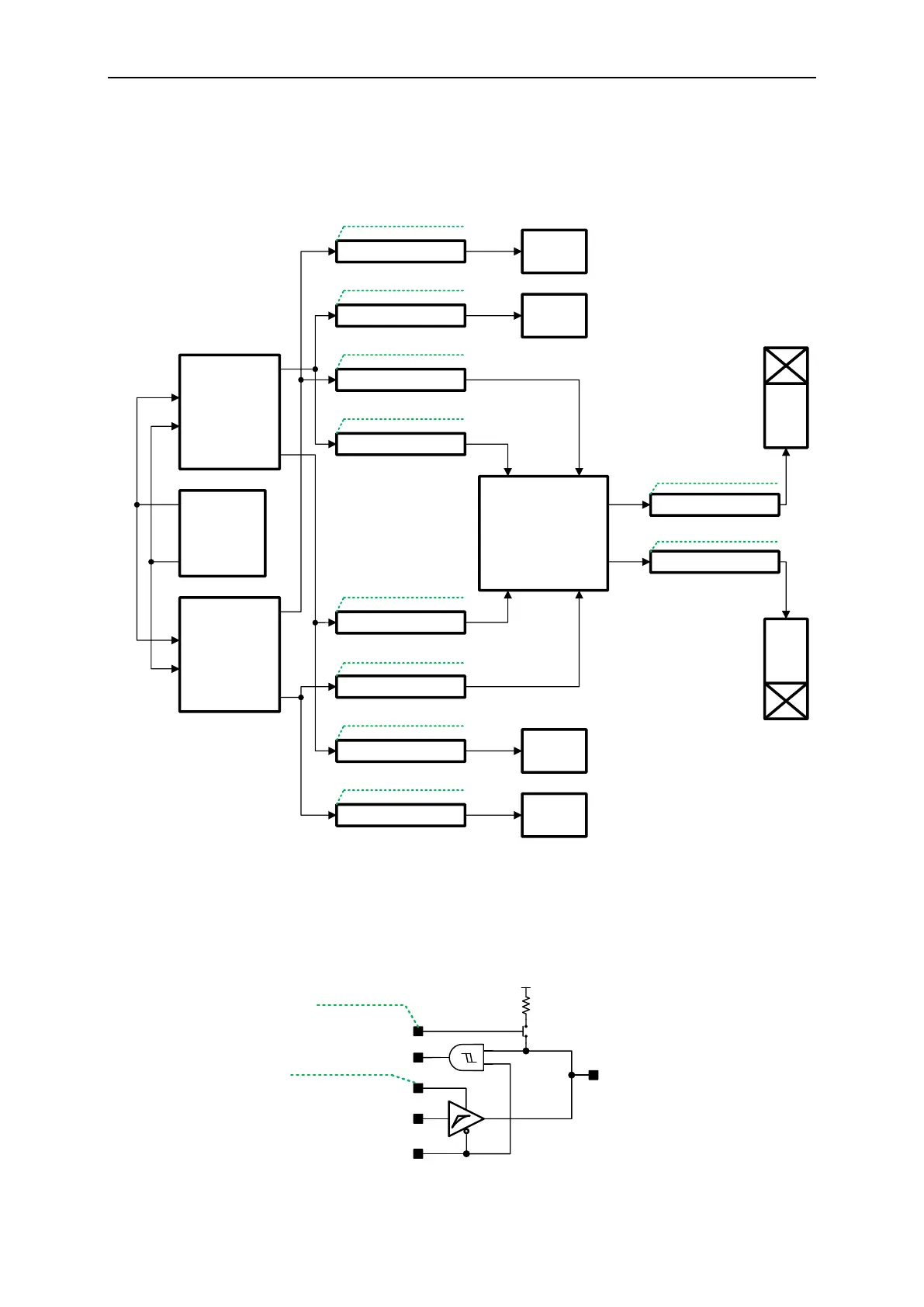

A2.12 IO Cell Control Diagram

PAD

PE

C

DS

I

DIR

Controllable from

configuration registers

Controllable from

configuration registers

Figure 21 IO cell and controllable parameters

Loading...

Loading...