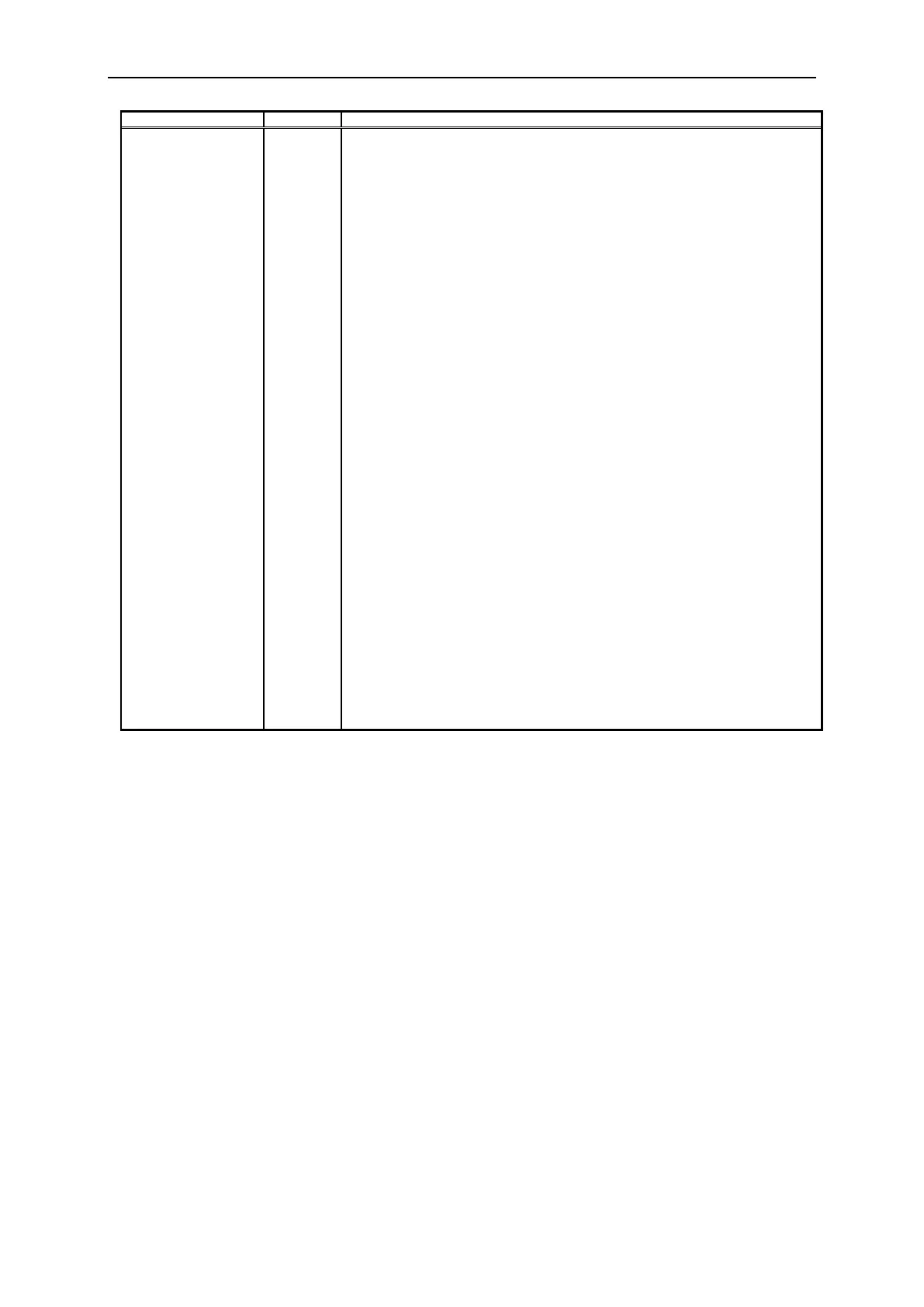

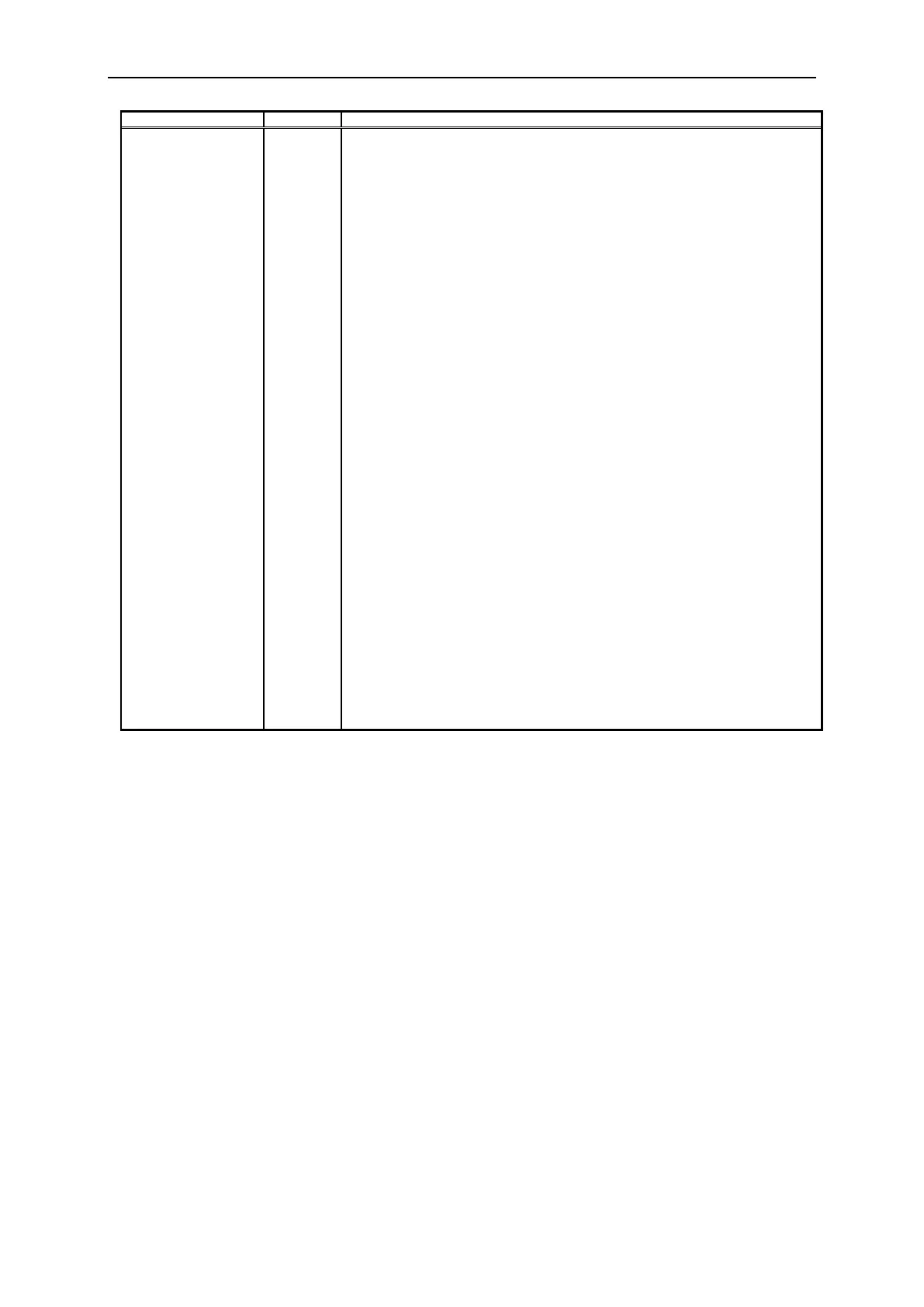

CDS_TXBTSP[1:0]: TX TSP B clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

CDS_TXATSP[1:0] : TX TSP A clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

CDS_RXBTSP[1:0]: RX TSP B clock delay.

00 – delay by 200ps (default)

01 – delay by 500ps

10 – delay by 800ps

11 – delay by 1100ps

CDS_RXATSP[1:0]: RX TSP A clock delay.

00 – delay by 200ps (default)

01 – delay by 500ps

10 – delay by 800ps

11 – delay by 1100ps

CDS_TXBLML[1:0]: TX LML B clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

CDS_TXALML[1:0]: TX LML A clock delay.

00 – delay by 400ps (default)

01 – delay by 500ps

10 – delay by 600ps

11 – delay by 700ps

CDS_RXBLML[1:0]: RX LML B clock delay.

00 – delay by 200ps (default)

01 – delay by 500ps

10 – delay by 800ps

11 – delay by 1100ps

CDS_RXALML[1:0]: RX LML A clock delay.

00 – delay by 200ps (default)

01 – delay by 500ps

10 – delay by 800ps

11 – delay by 1100ps

Default: 00000000 00000000

Loading...

Loading...