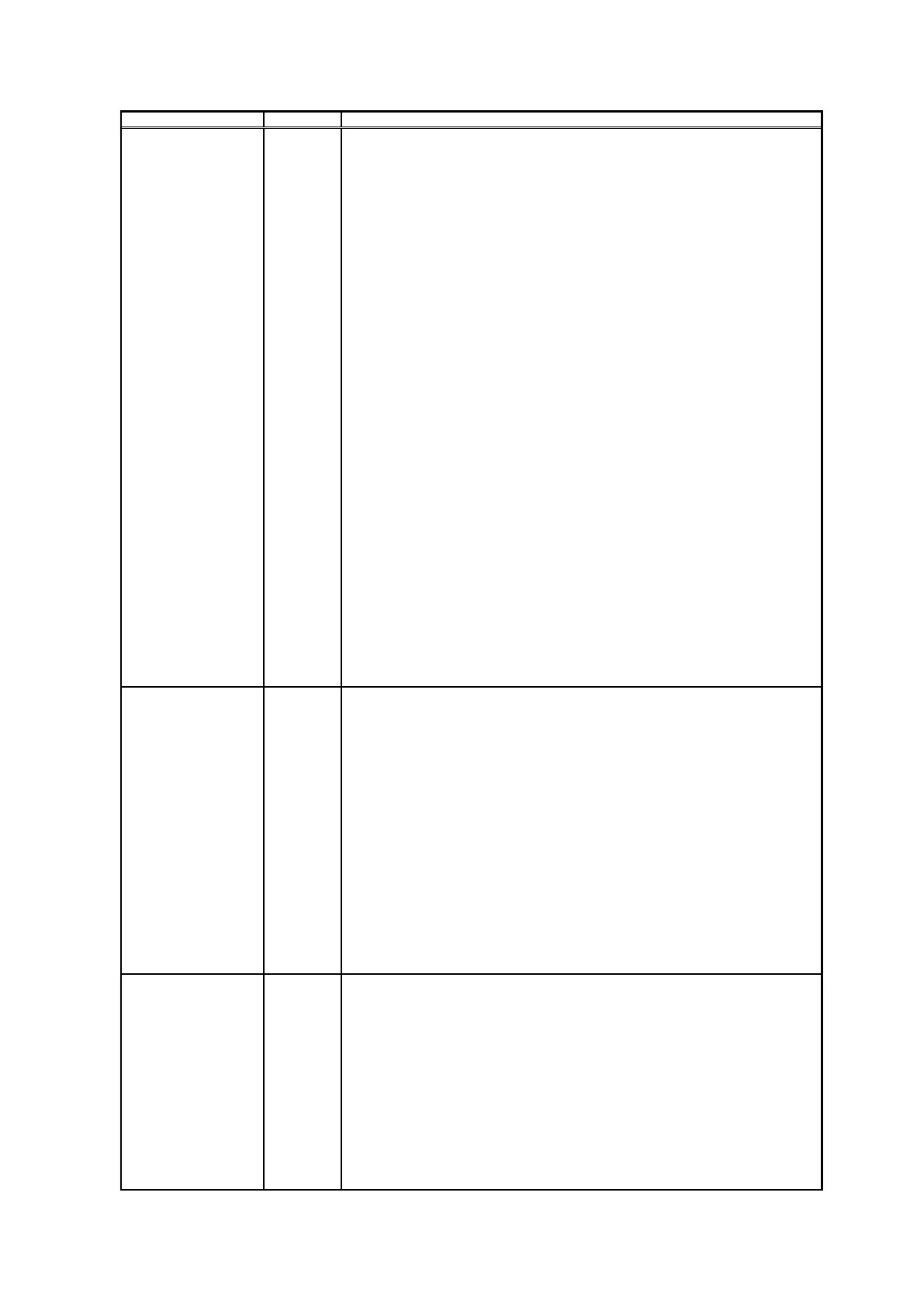

REV_SDMCLK_CGEN: Reverses the SDM clock

0 – default (default)

1 – reversed (after INV)

SEL_SDMCLK_CGEN: Selects between the feedback divider output and Fref for

SDM

0 – CLK CLK_DIV (default)

1 – CLK CLK_REF

SX_DITHER_EN_CGEN: Enabled dithering in SDM

0 – Disabled (default)

1 – Enabled

CLKH_OV_CLKL_CGEN[1:0]: FCLKL here is ADC clock. FCLKH is the clock to the

DAC and if no division is added to the ADC as well. Default: 0

FCLKL=FCLKH/2^(CLKH_OV_CLKL)

DIV_OUTCH_CGEN[7:0]: Controls the output divider chain of the CGEN.

F_CLKH=Fvco_CGEN/(2*(DIV_OUTCH_CGEN+1)) Shadow register.

Default: 4

TST_CGEN[2:0]: Controls the test mode of the SX

0 – TST disabled; RSSI analog outputs enabled if RSSI blocks active and

when all PLL test signals are off (default)

1 – tstdo[0]=ADC clock; tstdo[1]=DAC clock; tstao = High impedance;

2 – tstdo[0]=SDM clock; tstdo[1]= feedback divider output; tstao = VCO

tune through a 60kOhm resistor;

3 – tstdo[0]=Reference clock; tstdo[1]= feedback divider output; tstao =

VCO tune through a 10kOhm resistor;

4 – tstdo[0]= High impedance; tstdo[1]= High impedance; tstao = High

impedance;

5 – tstdo[0]=Charge pump Down signal; tstdo[1]=Charge pump Up signal;

tstao = High impedance;

6 – tstdo[0]= High impedance; tstdo[1]= High impedance; tstao = VCO

tune through a 60kOhm resistor;

7 – tstdo[0]= High impedance; tstdo[1]= High impedance; tstao = VCO

tune through a 10kOhm resistor;

if TST_SX[2]=1 --> VCO_TSTBUF active generating VCO_TST_DIV20

and VCO_TST_DIV40

Default: 00000000 00100000

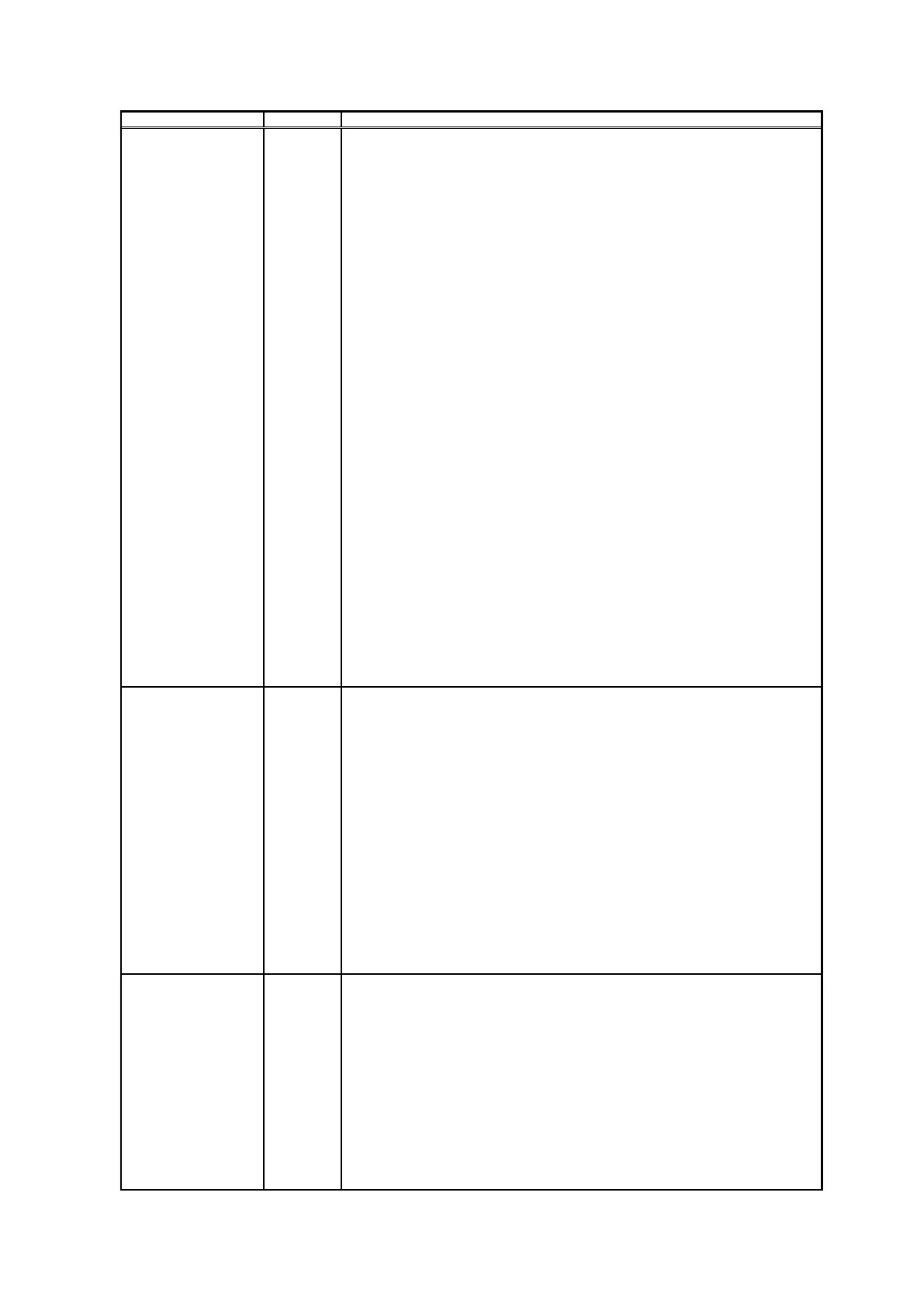

Reserved

REV_CLKDAC_CGEN: Inverts the clock F_CLKL.

0 – Normal (default)

1 – Inverted

REV_CLKADC_CGEN: Inverts the clock F_CLKL.

0 – Normal (default)

1 – Inverted

REVPH_PFD_CGEN: Reverse the pulses of PFD. It can be used to reverse the

polarity of the PLL loop (positive feedback to negative feedback). Default: 0

IOFFSET_CP_CGEN[5:0]: Scales the offset current of the charge pump, 0-->63.

This current is used in Fran-N mode to create an offset in the CP response and

avoid the non-linear section. Default: 20

ioffset=0.243uA * IOFFSET_CP_SX

ioffset/ipulse=4/(INT_SDM_SX+4) [First estimation]

IPULSE_CP_CGEN[5:0]: Scales the pulse current of the charge pump, 0-->63.

Default: 20

ipulse=2.312uA * IPULSE_CP_SX

Default: 00000101 00010100

Reserved

CMPLO_CTRL_CGEN: Controls the CGEN PLL VCO comparator low treshold

value:

0 – Low treshold is set to 0.18V (Default)

1 – Low treshold is set to 0.1V

ICT_VCO_CGEN[4:0]: Scales the VCO bias current from 0 to 2.5xInom. Default: 15

CSW_VCO_CGEN[7:0]: coarse control of VCO frequency, 0 for lowest frequency

and 255 for highest. This control is set by SX_SWC_calibration. Shadow register.

Default: 128

COARSE_START_CGEN: Control signal for coarse tuning algorithm

(SX_SWC_calibration). Default: 0

Default: 00011111 00000000

Loading...

Loading...