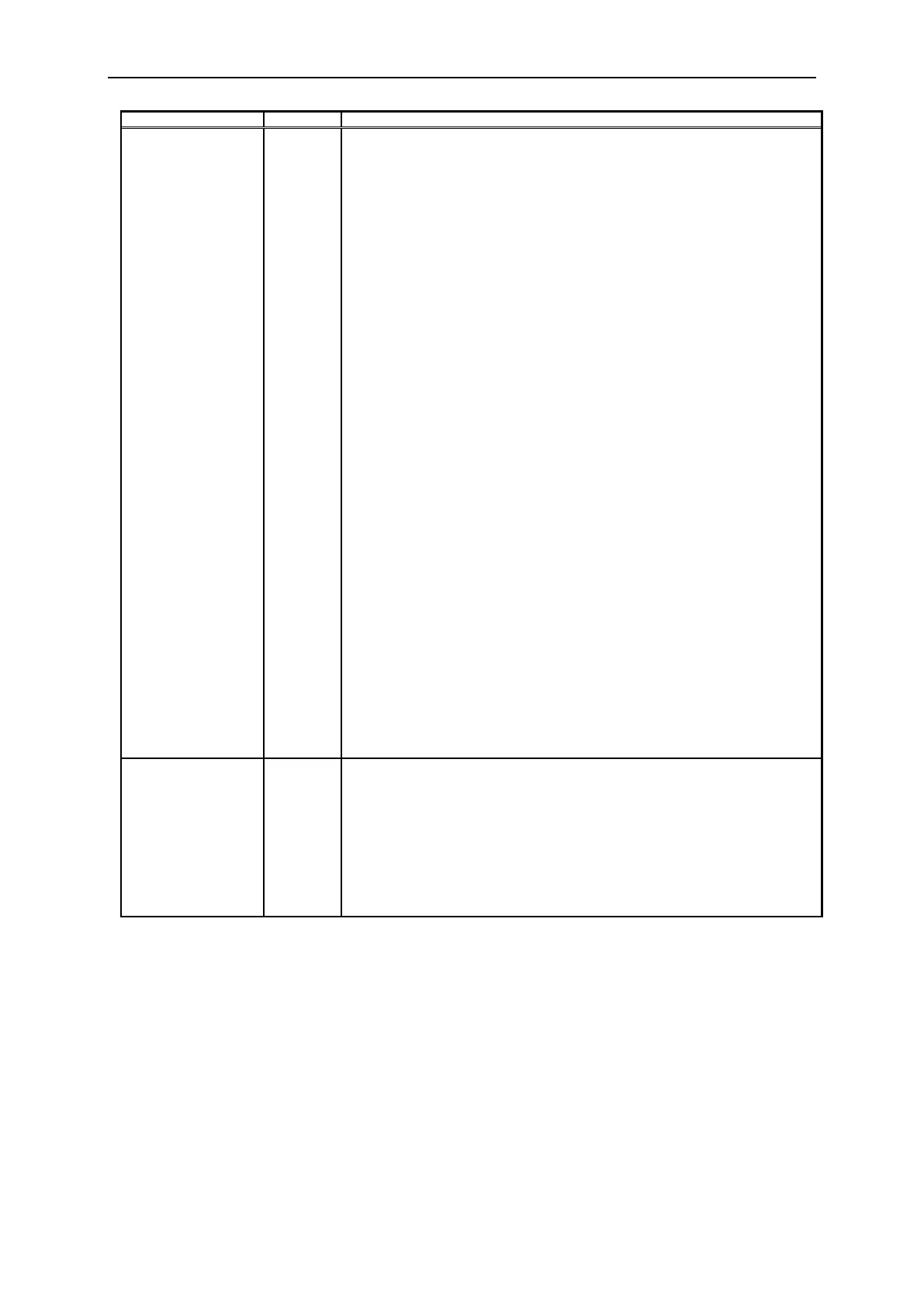

CMIX_GAIN[1:0]: Gain of CMIX output, least significant part.

CMIX_GAIN[2] CMIX_GAIN[1:0] CMIX output gain

============================================

0 (default) 00 (default) 0dB

0 01 +6dB

0 10, 11 –6dB

CMIX_SC: Spectrum control of CMIX.

1 – Downconvert

0 – Upconvert (default)

CMIX_GAIN[2]: Gain of CMIX output, most significant part.

CMIX_GAIN[2] CMIX_GAIN[1:0] CMIX output gain

============================================

1 00 +3dB

1 01, 10, 11 -3dB

Reserved

DCLOOP_STOP: RxDC tracking loop stop.

1 – Loop is stopped

0 – Use (default)

CMIX_BYP: CMIX bypass.

1 – Bypass

0 – Loop is active (default)

AGC_BYP: AGC bypass.

1 – Bypass

0 – Use (default)

GFIR3_BYP: GFIR3 bypass.

1 – Bypass

0 – Use (default)

GFIR2_BYP: GFIR2 bypass.

1 – Bypass

0 – Use (default)

GFIR1_BYP: GFIR1 bypass.

1 – Bypass

0 – Use (default)

DC_BYP: DC corrector bypass.

1 – Bypass

0 – Use (default)

GC_BYP: Gain corrector bypass.

1 – Bypass

0 – Use (default)

PH_BYP: Phase corrector bypass.

1 – Bypass

0 – Use (default)

Default: 00000000 00000000

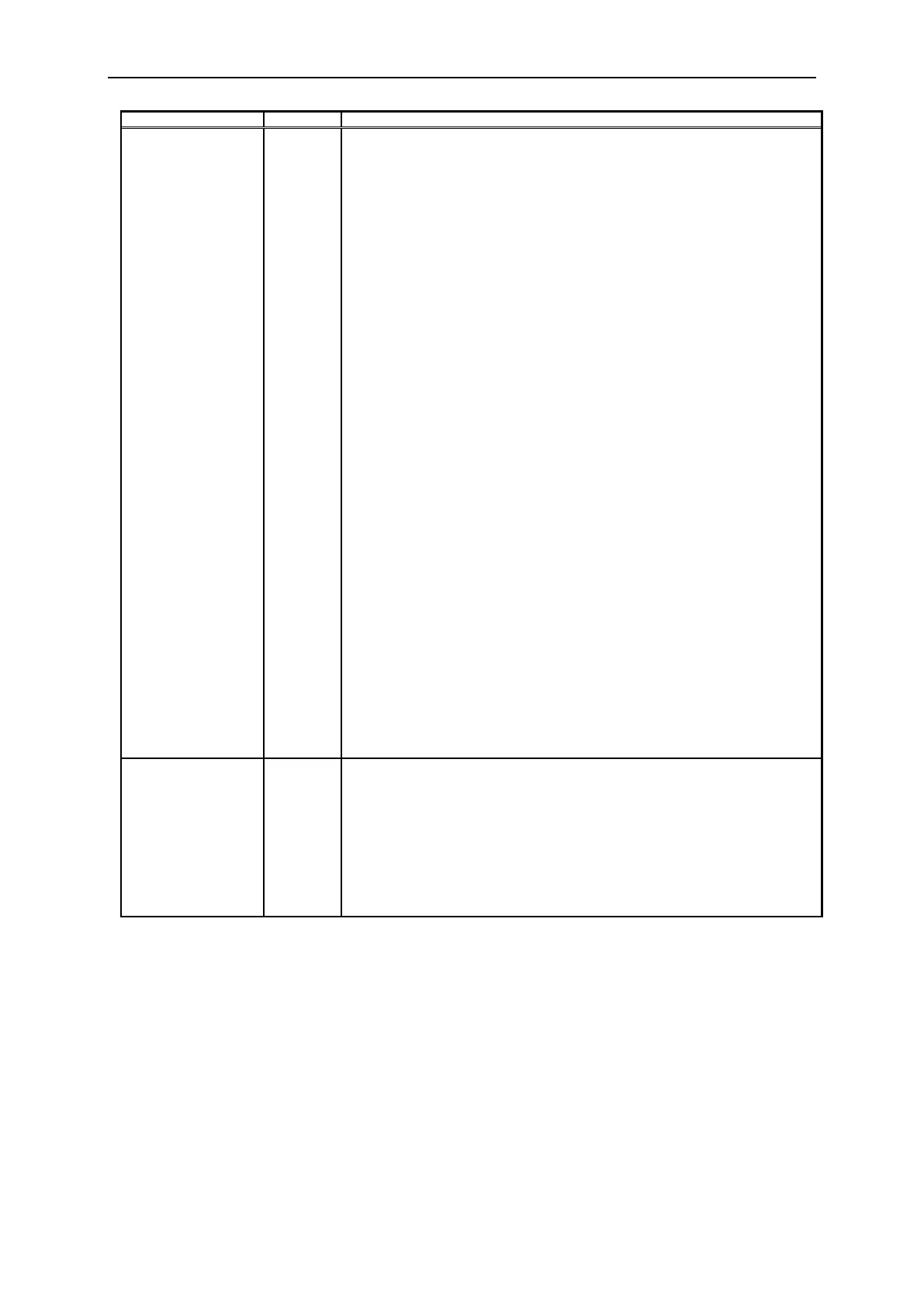

CAPD[31:0]: Data capture register. Stores data, selected by CAPSEL[1:0], on rising

edge of CAPTURE. Register layout is as follows:

CAPSEL_ADC CAPSEL[1:0] 0x040E, 0x040F

=======================================================

0 00 0s, RSSI[1:0] RSSI[17:2]

0 01 0s, ADCI_i[9:0] 0s, ADCQ_i[9:0]

1 XX ADCI_o[15:0] ADCQ_o[15:0]

0 10 BISTI[14:0], BSTATE 0s, BISTI[22:15]

0 11 BISTQ[14:0], BSTATE 0s, BISTQ[22:15]

Read only

Loading...

Loading...