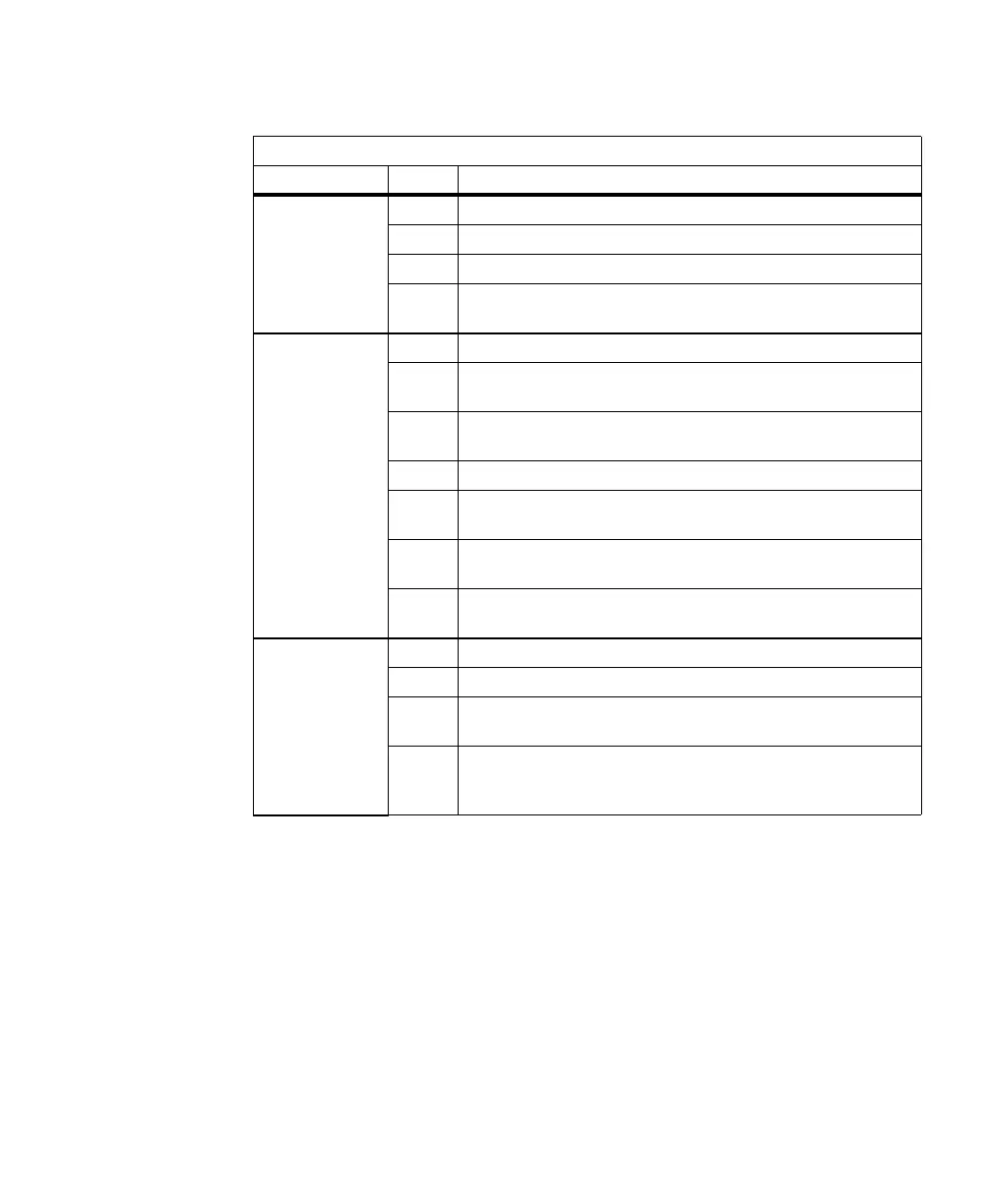

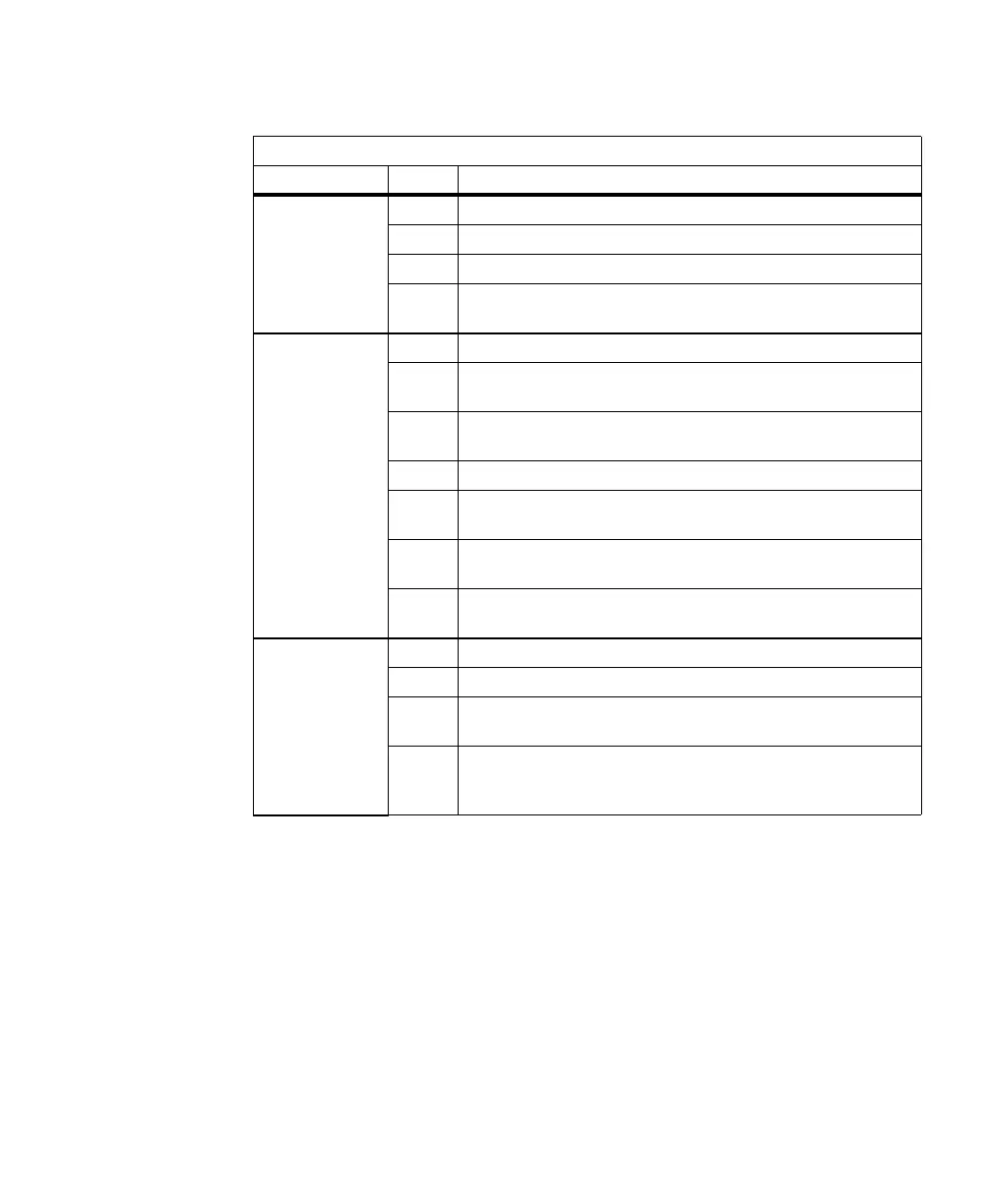

166 Appendix C: Major revisions of Matrox Solios boards

RoHS-compliant versions of Matrox Solios eCL/XCL

Part number Version Description

SOL6MCL* 100 First shipping version.

101 Set a default clock speed to improve testability.

102 Changed product packaging.

103 Changed a TTL buffer of a TTL auxiliary output signal to one with a higher

voltage tolerance. This was a preventive action.

SOL6MCLE* 100 First shipping version.

101 Upgraded the PCI-X to PCIe bridge to a new version. This was a corrective

action. For more information, refer to product bulletin MIPB-67.

104 Modified the power-up sequence of the PCIe bridge. This was a corrective

action. For more information, refer to product bulletin MIPB-77.

105 Changed product packaging.

106 Added pull-up resistors to the interface of the CPLD. This was a corrective

action. For more information, refer to product bulletin MIPB-95.

107 Replaced a pull-up resistor so that stronger PCIe interrupt signals could be

transmitted. This was a preventive action.

108 Upgraded the PCI-X to PCIe bridge to a new version. This was done to

ensure availability.

SOL6MFC* 100 First shipping version.

101 Changed product packaging.

102 Changed a TTL buffer of a TTL auxiliary output signal to one with a higher

voltage tolerance. This was a preventive action.

103 Replaced the LVDS receiver to support 5 V LVDS auxiliary input signals

(required to support most rotary encoders). This was done to enhance the

feature set. For more information, refer to product bulletin MIPB-56.

Loading...

Loading...