LPC5411x All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2018. All rights reserved.

Product data sheet Rev. 2.1 — 9 May 2018 50 of 105

NXP Semiconductors

LPC5411x

32-bit ARM Cortex-M4/M0+ microcontroller

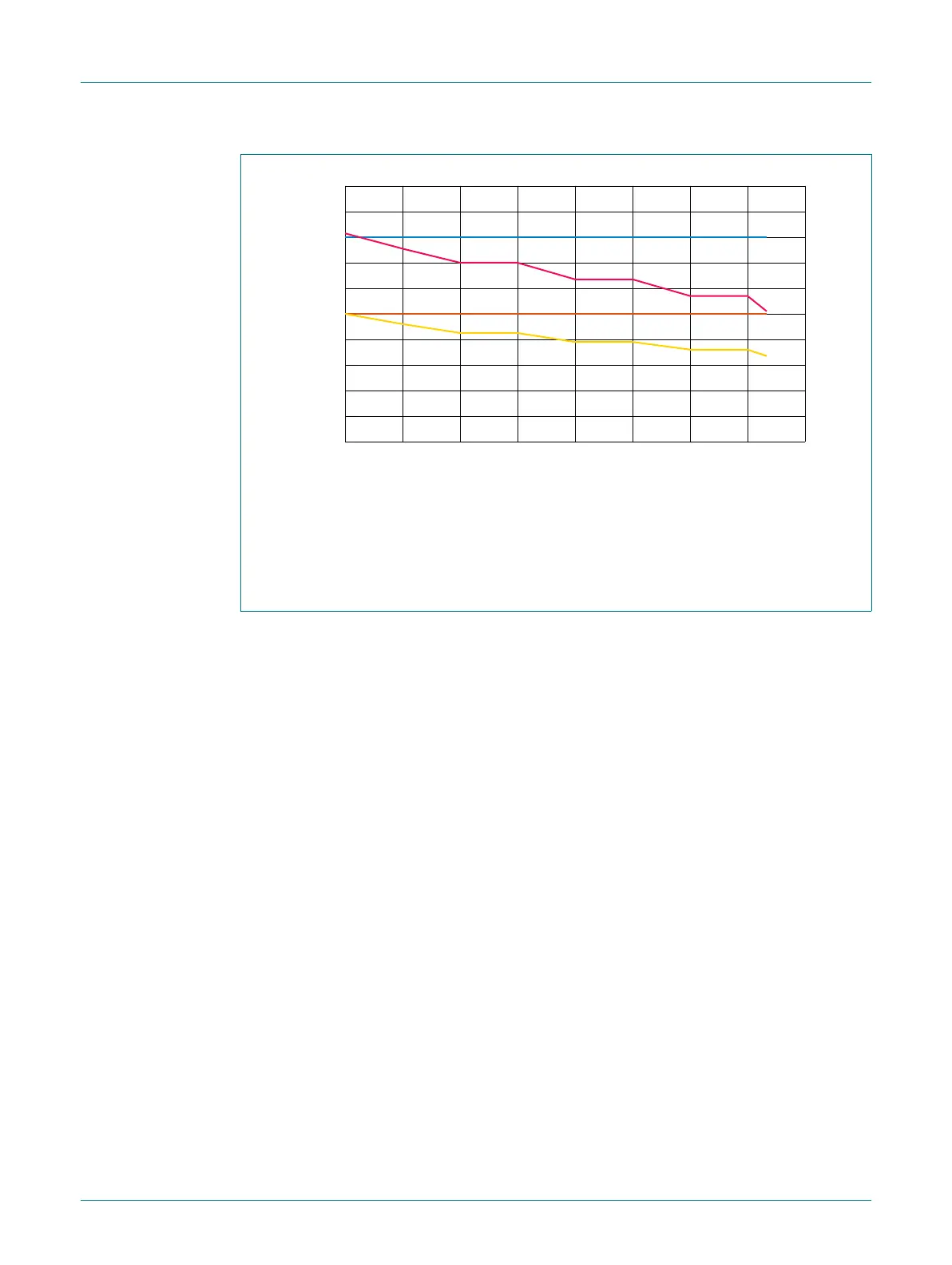

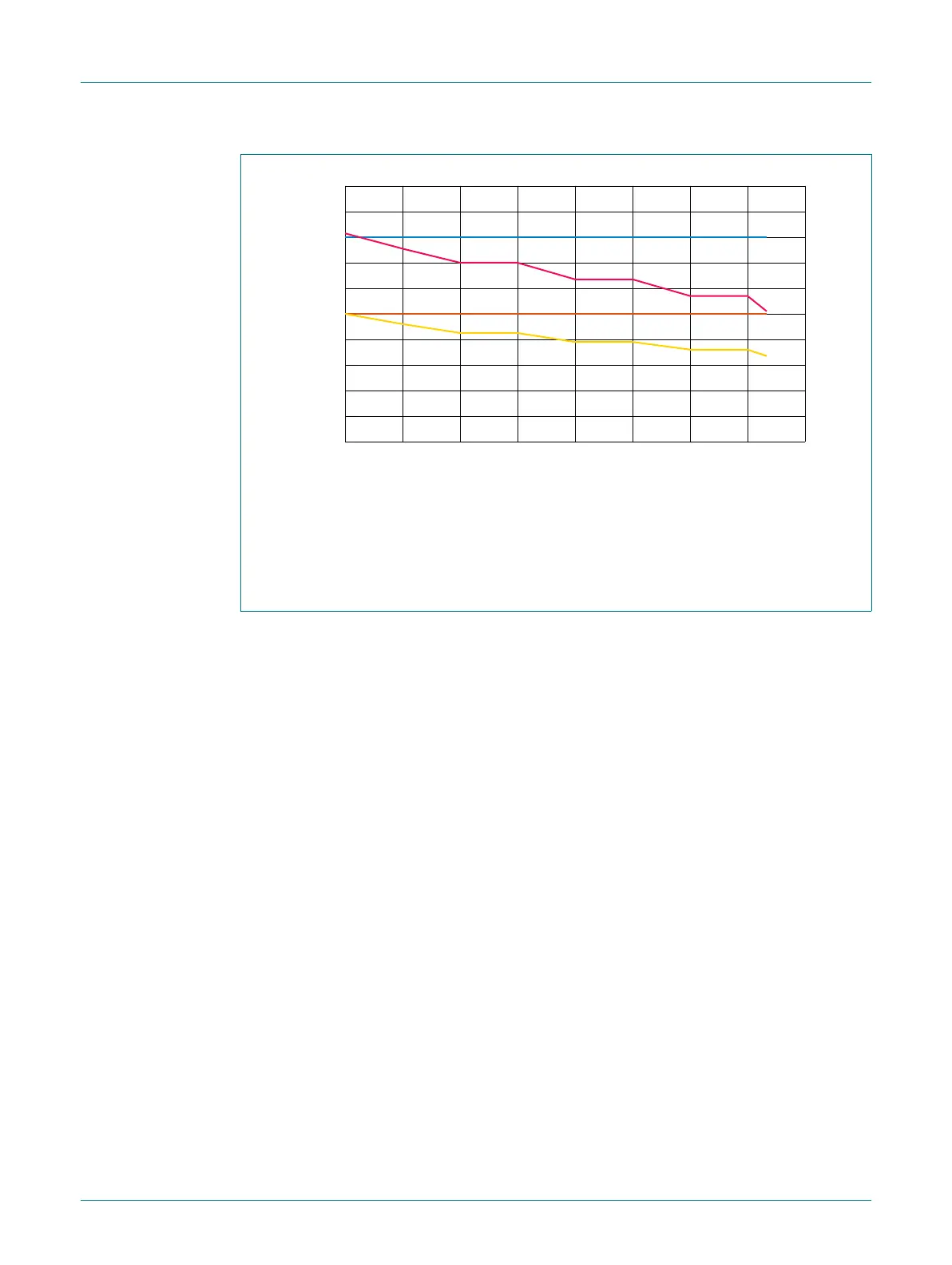

Conditions: V

DD

= 3.3 V; T

amb

= 25 °C; active mode; all peripherals disabled; BOD disabled; See

the FLASHCFG register in the LPC5411x, UM10914 User Manual for system clock flash access

time settings. Measured with Keil uVision 5.17. Optimization level 3, optimized for time ON.

12 MHz, 48 MHz, and 96 MHz: FRO enabled; PLL disabled.

24 MHz, 36 MHz, 60 MHz, 72 MHz, 84 MHz, and 100 MHz: FRO enabled; PLL enabled.

Fig 9. Typical CoreMark score

DDD

)UHTXHQF\0+]

&RUHPDUNVFRUH

&RUHPDUNVFRUH&RUHPDUNVFRUH

LWHUDWLRQVV0+]

LWHUDWLRQVV0+]LWHUDWLRQVV0+]

065$0065$0065$0

0)ODVK

0)ODVK0)ODVK

065$0

065$0065$0

0)ODVK

0)ODVK0)ODVK

Loading...

Loading...