LPC5411x All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2018. All rights reserved.

Product data sheet Rev. 2.1 — 9 May 2018 72 of 105

NXP Semiconductors

LPC5411x

32-bit ARM Cortex-M4/M0+ microcontroller

11.10 SPI interfaces

The actual SPI bit rate depends on the delays introduced by the external trace, the

external device, system clock (CCLK), and capacitive loading. Excluding delays

introduced by external device and PCB, the maximum supported bit rate for SPI master

mode is 48 Mbit/s, and the maximum supported bit rate for SPI slave mode is 15 Mbit/s.

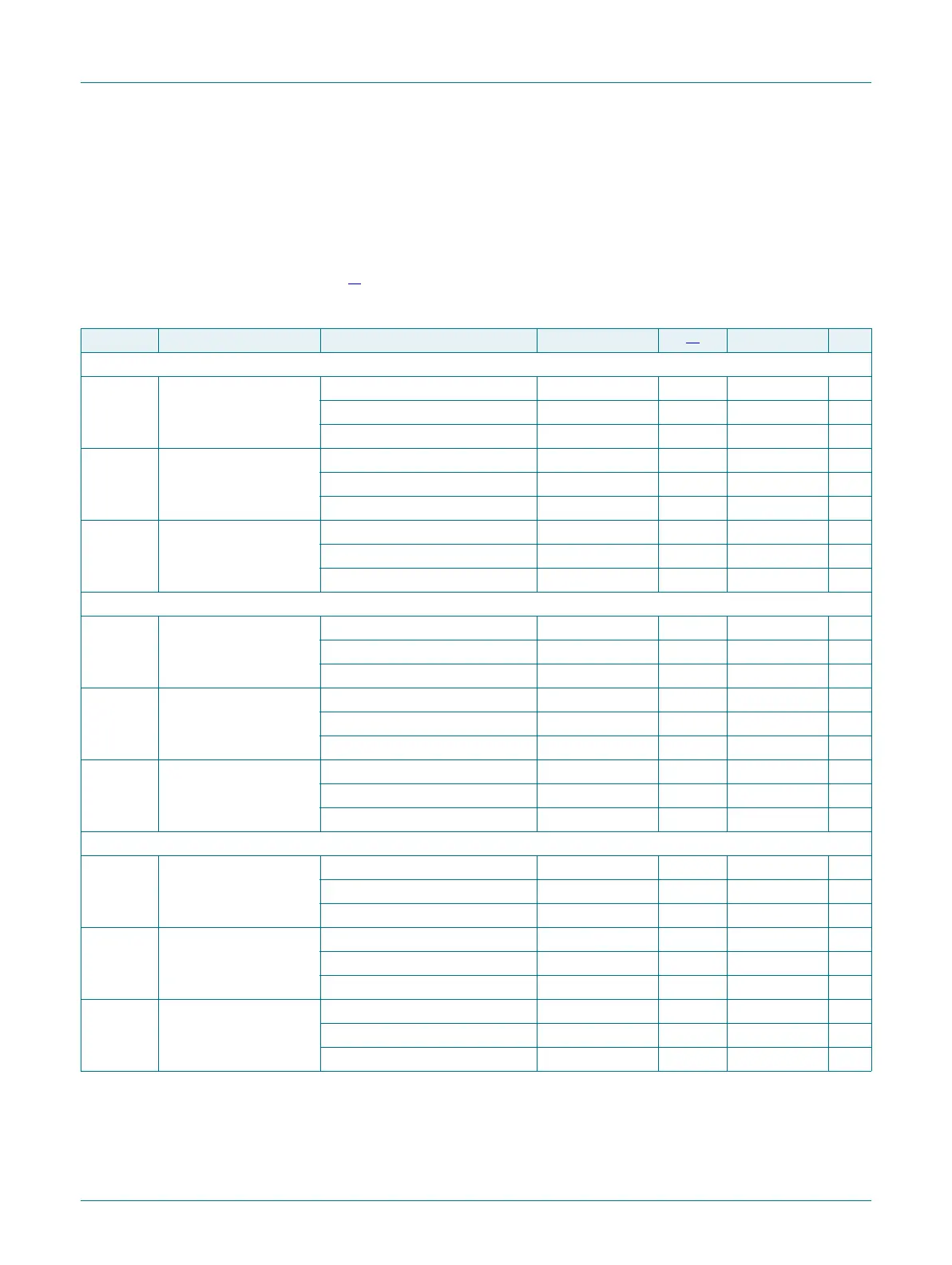

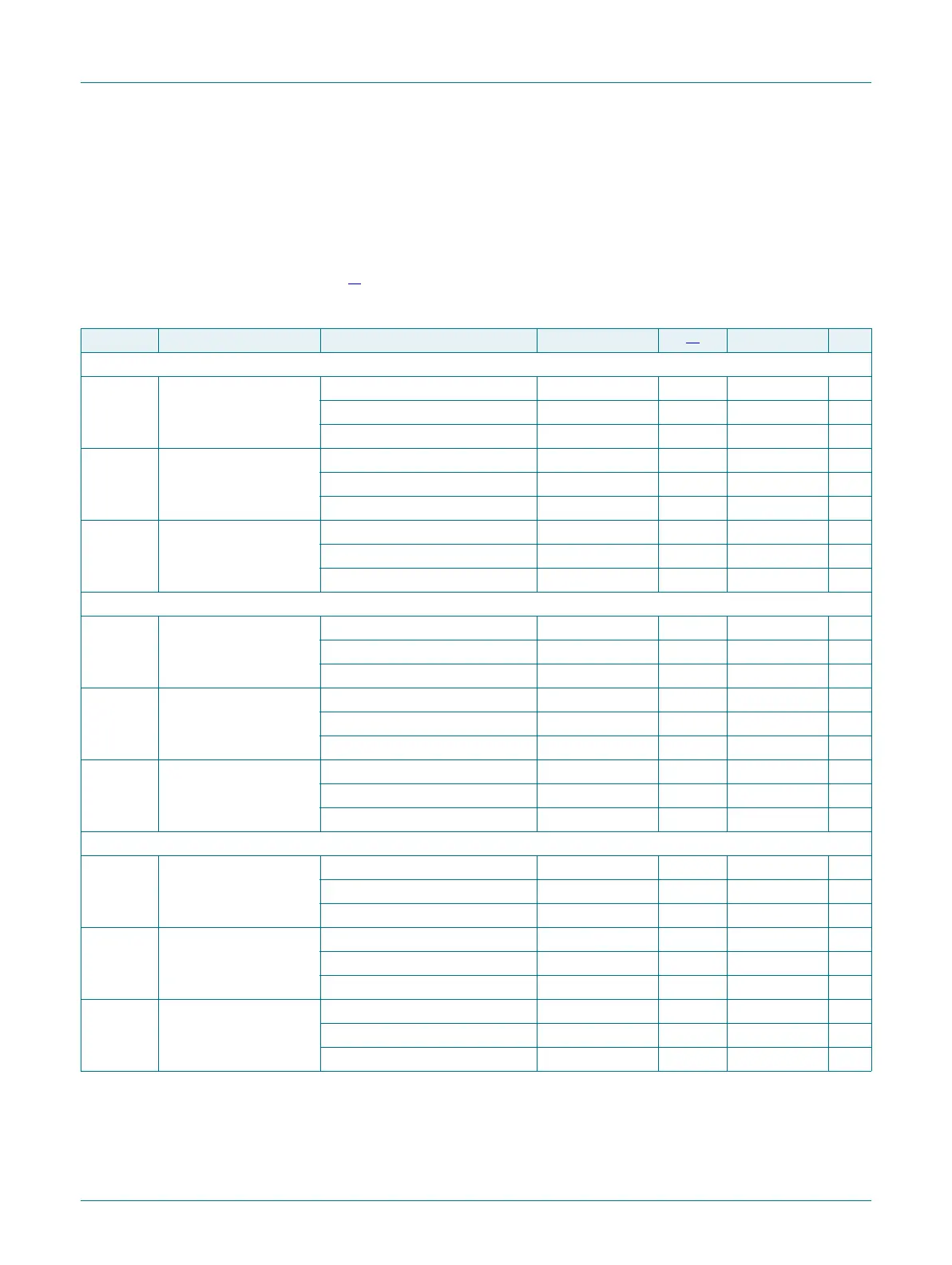

Table 31. SPI dynamic characteristics

[1]

T

amb

=

40

C to 105

C; V

DD

= 1.62 V to 3.6 V; C

L

= 30 pF balanced loading on all pins; Input slew = 1 ns, SLEW set to

standard mode for all pins; Parameters sampled at the 90 % and 10 % level of the rising or falling edge.

Symbol Parameter Conditions Min Typ

[2]

Max Unit

SPI master 1.62 V V

DD

2.0 V

t

DS

data set-up time CCLK = 1 MHz to 12 MHz 0 - - ns

CCLK = 48 MHz to 60 MHz 0 - - ns

CCLK = 96 MHz 0 - - ns

t

DH

data hold time CCLK = 1 MHz to 12 MHz 7 - - ns

CCLK = 48 MHz to 60 MHz 7 - - ns

CCLK = 96 MHz 7 - - ns

t

v(Q)

data output valid time CCLK = 1 MHz to 12 MHz 0 - 5 ns

CCLK = 48 MHz to 60 MHz 0 - 3 ns

CCLK = 96 MHz 0 - 2 ns

SPI slave 1.62 V V

DD

2.0 V

t

DS

data set-up time CCLK = 1 MHz to 12 MHz 1 - - ns

CCLK = 48 MHz to 60 MHz 1 - - ns

CCLK = 96 MHz 1 - - ns

t

DH

data hold time CCLK = 1 MHz to 12 MHz 2 - - ns

CCLK = 48 MHz to 60 MHz 3 - - ns

CCLK = 96 MHz 3 - - ns

t

v(Q)

data output valid time CCLK = 1 MHz to 12 MHz 30 - 58 ns

CCLK = 48 MHz to 60 MHz 23 - 48 ns

CCLK = 96 MHz 21 - 45 ns

SPI master 2.7 V V

DD

3.6 V

t

DS

data set-up time CCLK = 1 MHz to 12 MHz 3 - - ns

CCLK = 48 MHz to 60 MHz 4 - - ns

CCLK = 96 MHz 4 - - ns

t

DH

data hold time CCLK = 1 MHz to 12 MHz 11 - - ns

CCLK = 48 MHz to 60 MHz 11 - - ns

CCLK = 96 MHz 10 - - ns

t

v(Q)

data output valid time CCLK = 1 MHz to 12 MHz 0 - 5 ns

CCLK = 48 MHz to 60 MHz 0 - 3 ns

CCLK = 96 MHz 0 - 3 ns

Loading...

Loading...