LPC5411x All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2018. All rights reserved.

Product data sheet Rev. 2.1 — 9 May 2018 73 of 105

NXP Semiconductors

LPC5411x

32-bit ARM Cortex-M4/M0+ microcontroller

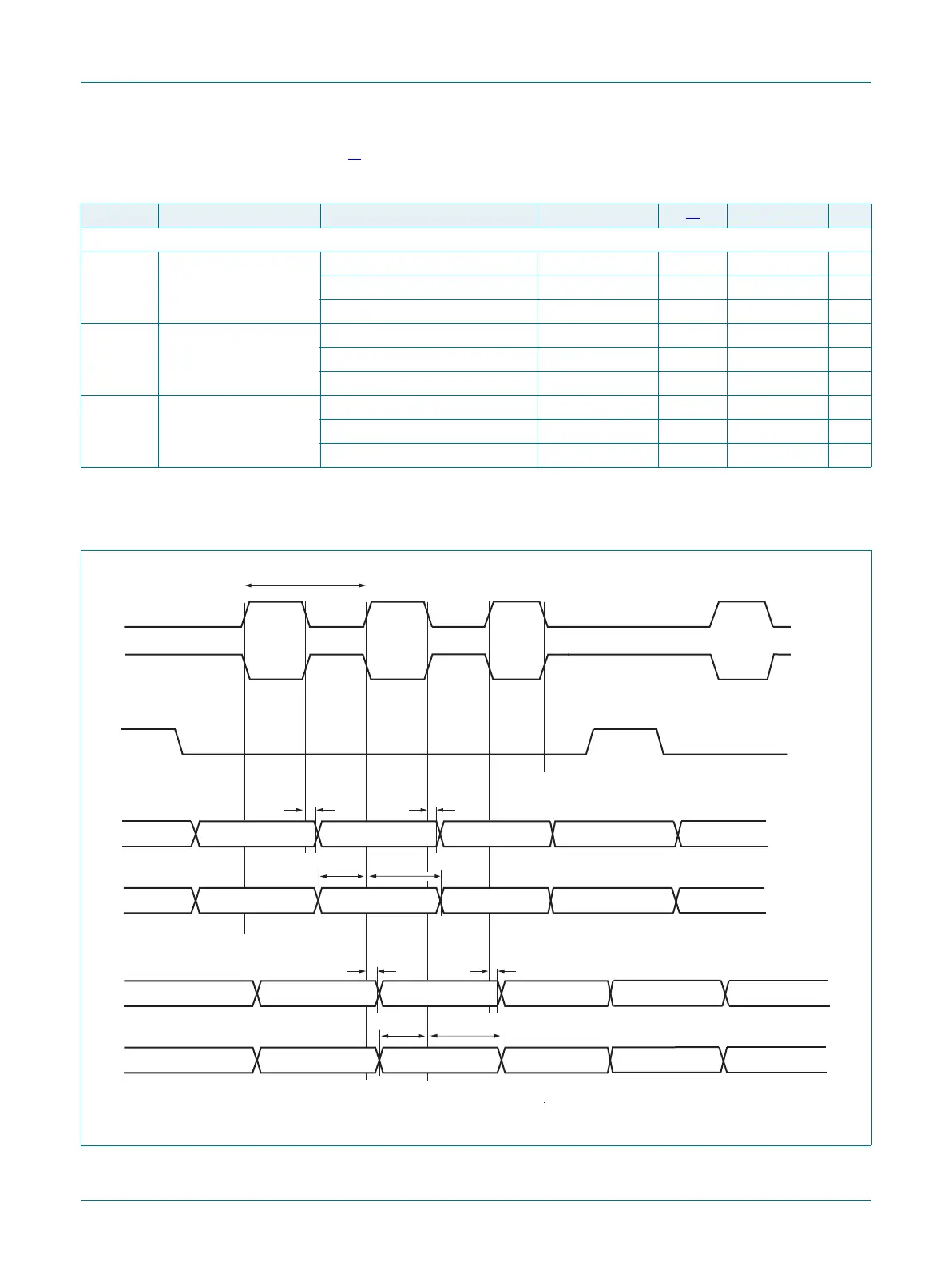

[1] Based on characterization; not tested in production.

[2] Typical ratings are not guaranteed.

SPI slave 2.7 V V

DD

3.6 V

t

DS

data set-up time CCLK = 1 MHz to 12 MHz 2 - - ns

CCLK = 48 MHz to 60 MHz 1 - - ns

CCLK = 96 MHz 1 - - ns

t

DH

data hold time CCLK = 1 MHz to 12 MHz 1 - - ns

CCLK = 48 MHz to 60 MHz 1 - - ns

CCLK = 96 MHz 1 - - ns

t

v(Q)

data output valid time CCLK = 1 MHz to 12 MHz 20 - 44 ns

CCLK = 48 MHz to 60 MHz 15 - 32 ns

CCLK = 96 MHz 13 - 30 ns

Table 31. SPI dynamic characteristics

[1]

T

amb

=

40

C to 105

C; V

DD

= 1.62 V to 3.6 V; C

L

= 30 pF balanced loading on all pins; Input slew = 1 ns, SLEW set to

standard mode for all pins; Parameters sampled at the 90 % and 10 % level of the rising or falling edge.

Symbol Parameter Conditions Min Typ

[2]

Max Unit

Fig 22. SPI master timing

SCK (CPOL = 0)

MOSI (CPHA = 1)

SSEL

MISO (CPHA = 1)

T

cy(clk)

t

DS

t

DH

t

v(Q)

DATA VALID (LSB) DATA VALID

t

v(Q)

SCK (CPOL = 1)

DATA VALID (LSB)

DATA VALID

MOSI (CPHA = 0)

MISO (CPHA = 0)

t

DS

t

DH

DATA VALID (MSB) DATA VALID (MSB)DATA VALID

DATA VALID (LSB)

DATA VALID (LSB)

t

v(Q)

DATA VALID (MSB)

DATA VALID

t

v(Q)

aaa-014969

DATA VALID (MSB)

DATA VALID (MSB)

DATA VALID (MSB)

DATA VALID (MSB)

IDLE

IDLE

IDLE

IDLE

DATA VALID (MSB)

Loading...

Loading...