117

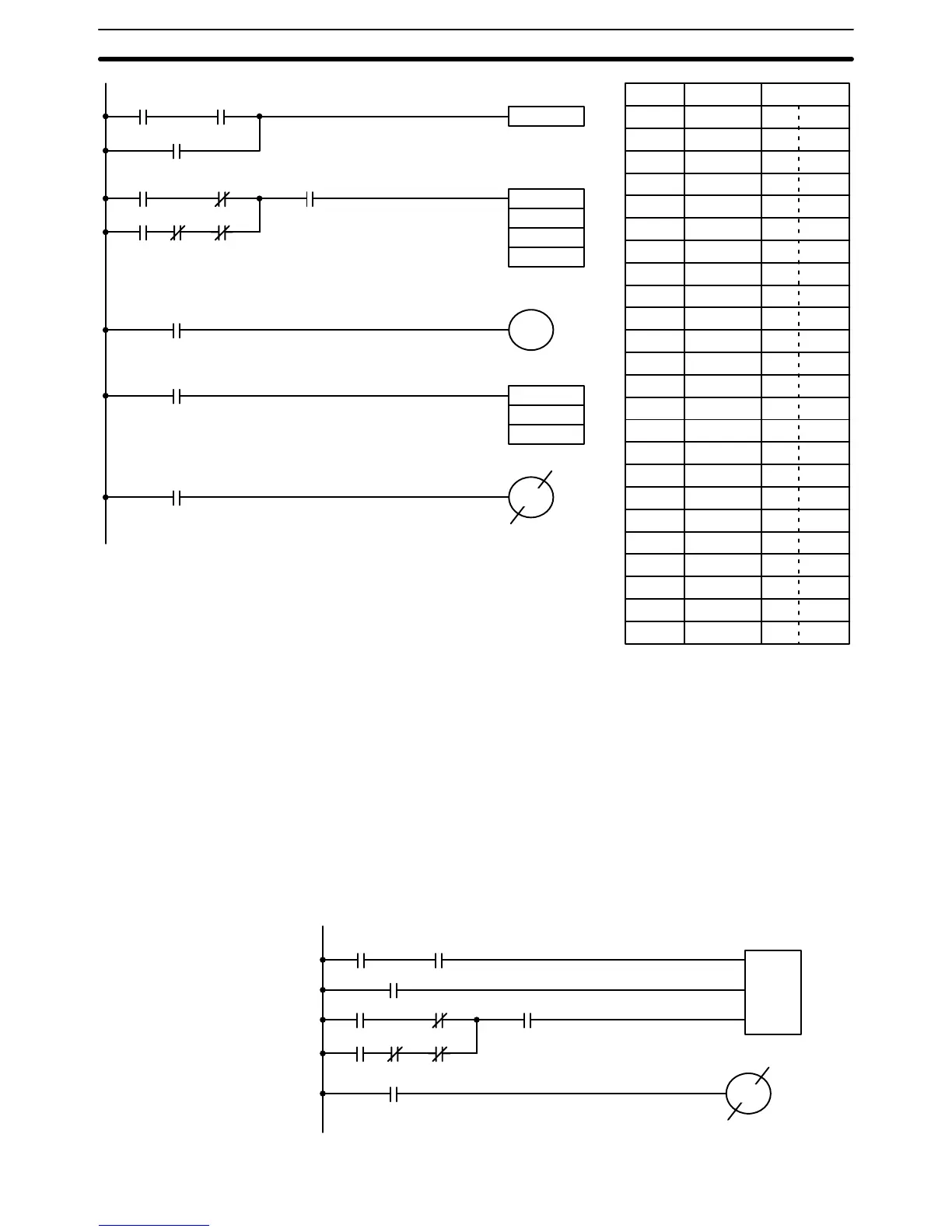

Address Instruction Data

0000 LD 0000

0001 AND 0001

0002 OR 0002

0003 DIFU(13) 1500

0004 LD 0100

0005 AND NOT 0200

0006 LD 0101

0007 AND NOT 0102

0008 AND NOT 1505

0009 OR LD ––

0010 AND 1500

0011 ADD(30) ––

# 0001

0004

HR 0

0012 LD 0005

0013 TIM 00

# 0150

0014 LD TIM 00

0015 MOV(21) ––

HR 0

HR 2

0016 LD HR 015

0017 OUT NOT 0500

0100 0200

DIFU(13) 1500

0500

TIM 00 # 15.0

ADD(30)

#0001

0004

HR 0

MOV(21)

HR 0

HR 2

0101 0102 1505

TIM 00

1500

0002

00005

HR 015

0000 0001

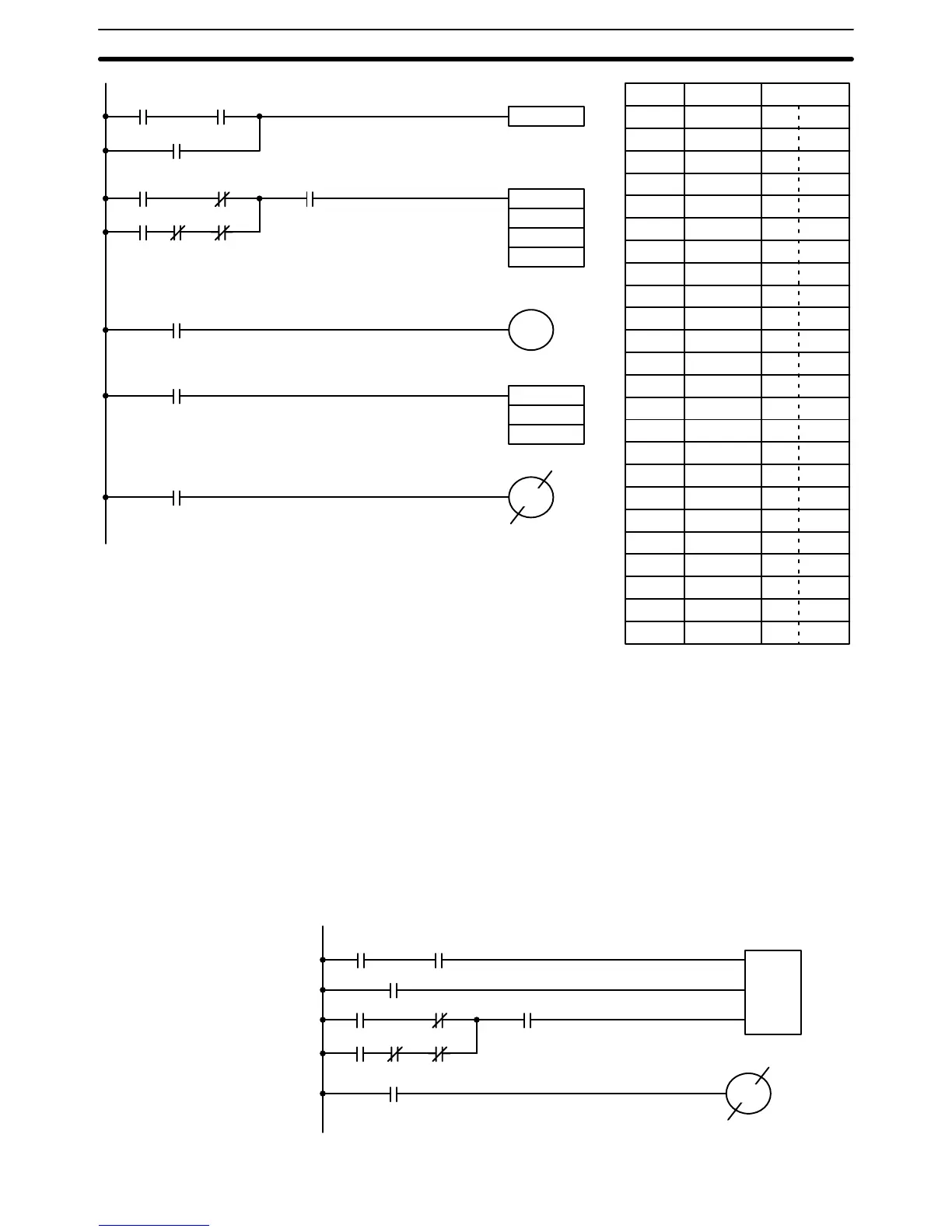

If a right-hand instruction requires multiple instruction lines, all of the lines for

the instruction are coded before the right-hand instruction. Each of the lines

for the instruction are coded starting with LD or LD NOT to form ‘logic

blocks’ that are combined by the right-hand instruction. An example of this for

CNTR(12) is shown below.

I

P

R

CNTR(12)

01

#5000

0100 0200

0500

0101 0102 1501

1500

0002

HR 015

0000 0001

Multiple Instruction Lines

Converting to Mnemonic Code Section 7–2

Loading...

Loading...