register, all conditions will be reported in the standard event summary

bit. At the moment, you have to write a decimal value by using the *ESE

command to set the enable register mask.

※

Note 1: The errors in the DMM’s error queue except reading the error

queue by using SYSTem:ERRor? will be recorded by an error condition

(including bits 2, 3, 4 or 5 of the standard event register).

※

Note 2: In both the standard event register bit 3 and the questionable

data event register bits 0, 1 or 9, a reading overload condition can be

reported all the time. But in the DMM’s error queue, no error message

will be recorded.

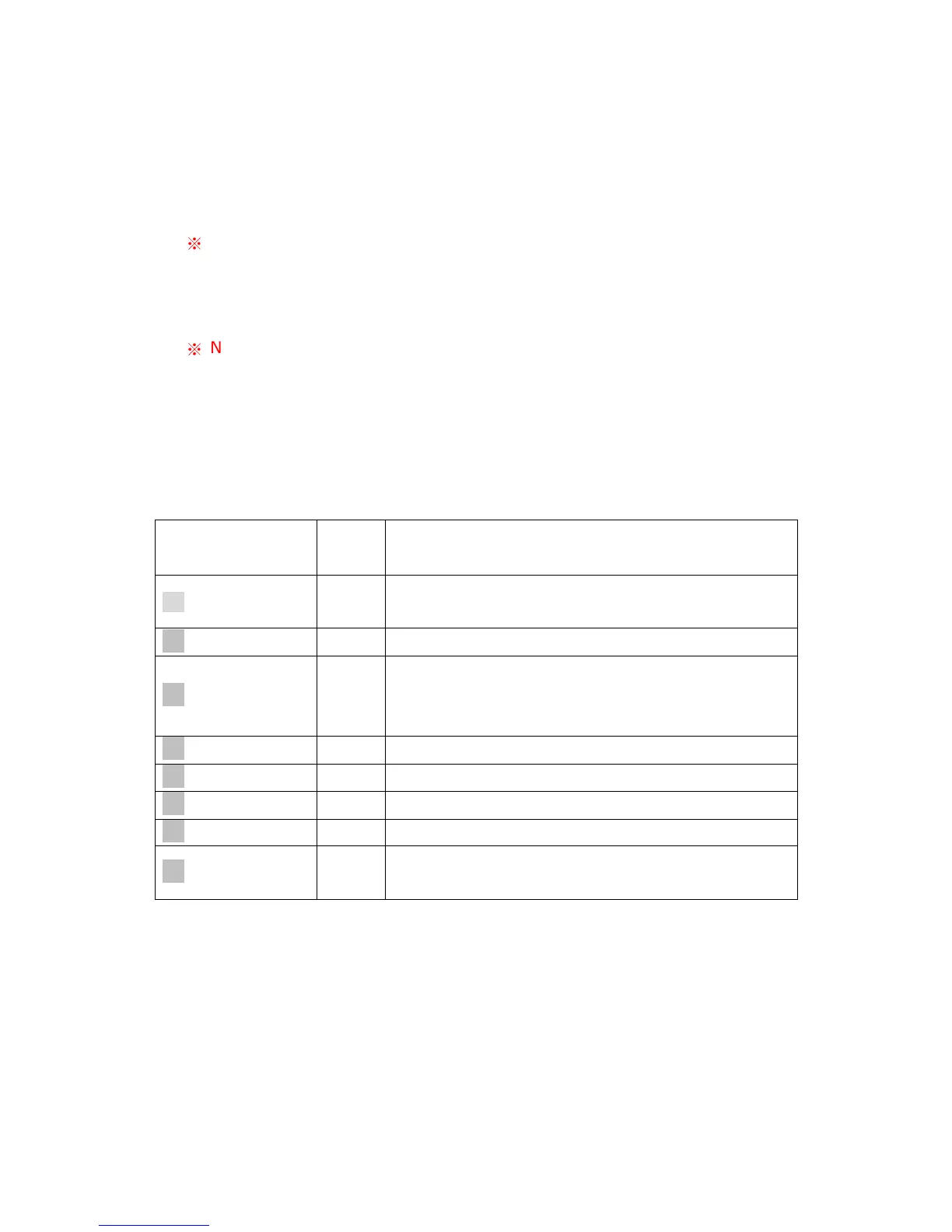

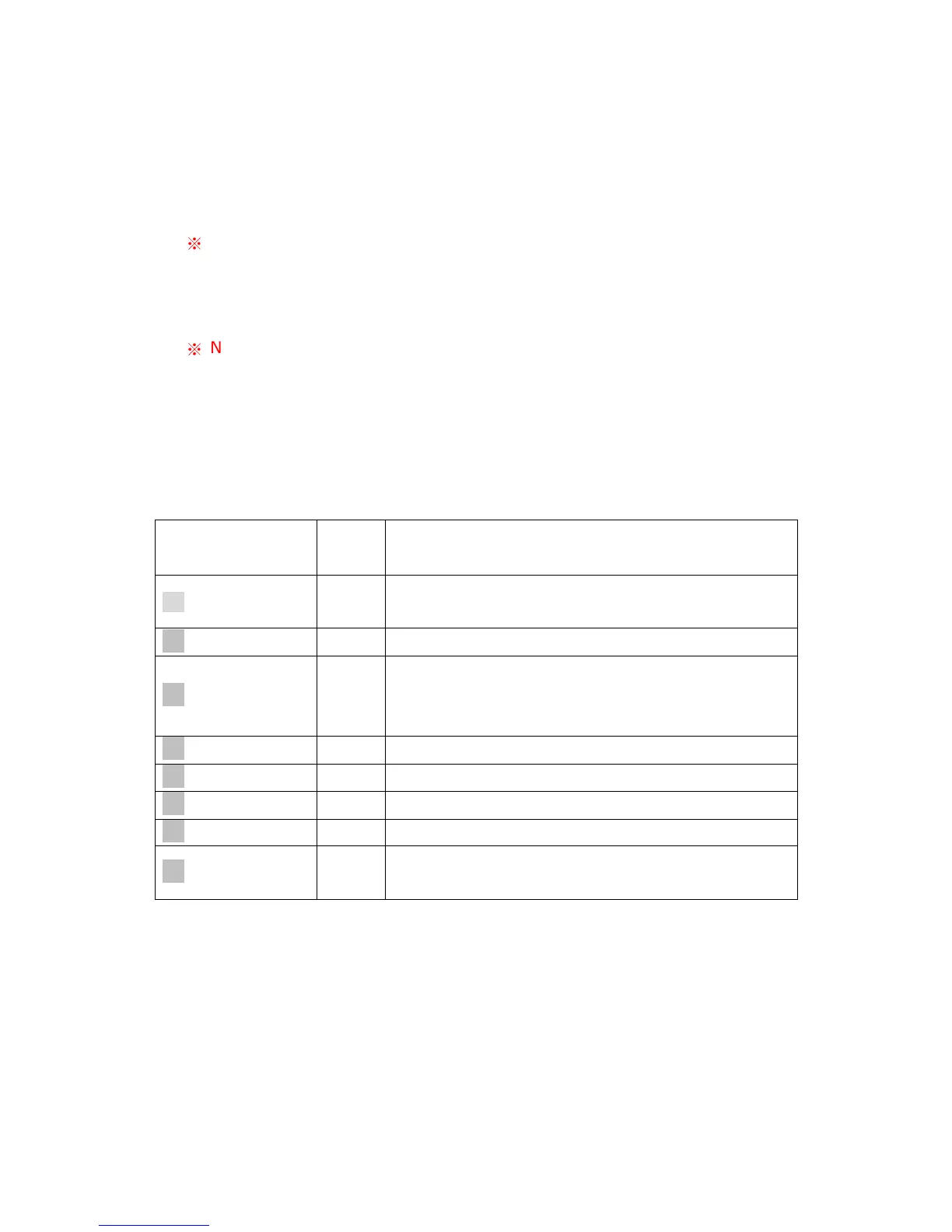

Bit Definitions for Standard Event Register

Bit

Decimal

Value

Definition

0.

Operation Complete

1

All commands prior to and including an *OPC command have been

executed

1.

Not Used

2

Set to 0.

2.

Query Error

4

The DMM output buffer was empty as the DMM tried to read from it.

Or a new command line was received before a previous query has

been read. Or, both the input and output buffers are full.

3.

Device Error

8 Error occurrence from a self-test, calibration or reading overlaod.

4.

Execution Error

16 Error occurrence from an execution.

5.

Command Error

32 Error occurrence from a command’s syntax.

6.

Not Used

64 Set to 0.

7.

Power On

128

Since the last time the event register was read or cleared, power has

been turned off and on.

The following conditions will clear the standard event register.

You send a *CLS command.

You query the event register by using the *ESR? command.

The following conditions will clear the standard event enable register.

You turn on the power, and have set the DMM previously by using

the *PSC 1 command.

Loading...

Loading...