R8C/20 Group, R8C/21 Group 10. Clock Generation Circuit

Rev.2.00 Aug 27, 2008 Page 84 of 458

REJ09B0250-0200

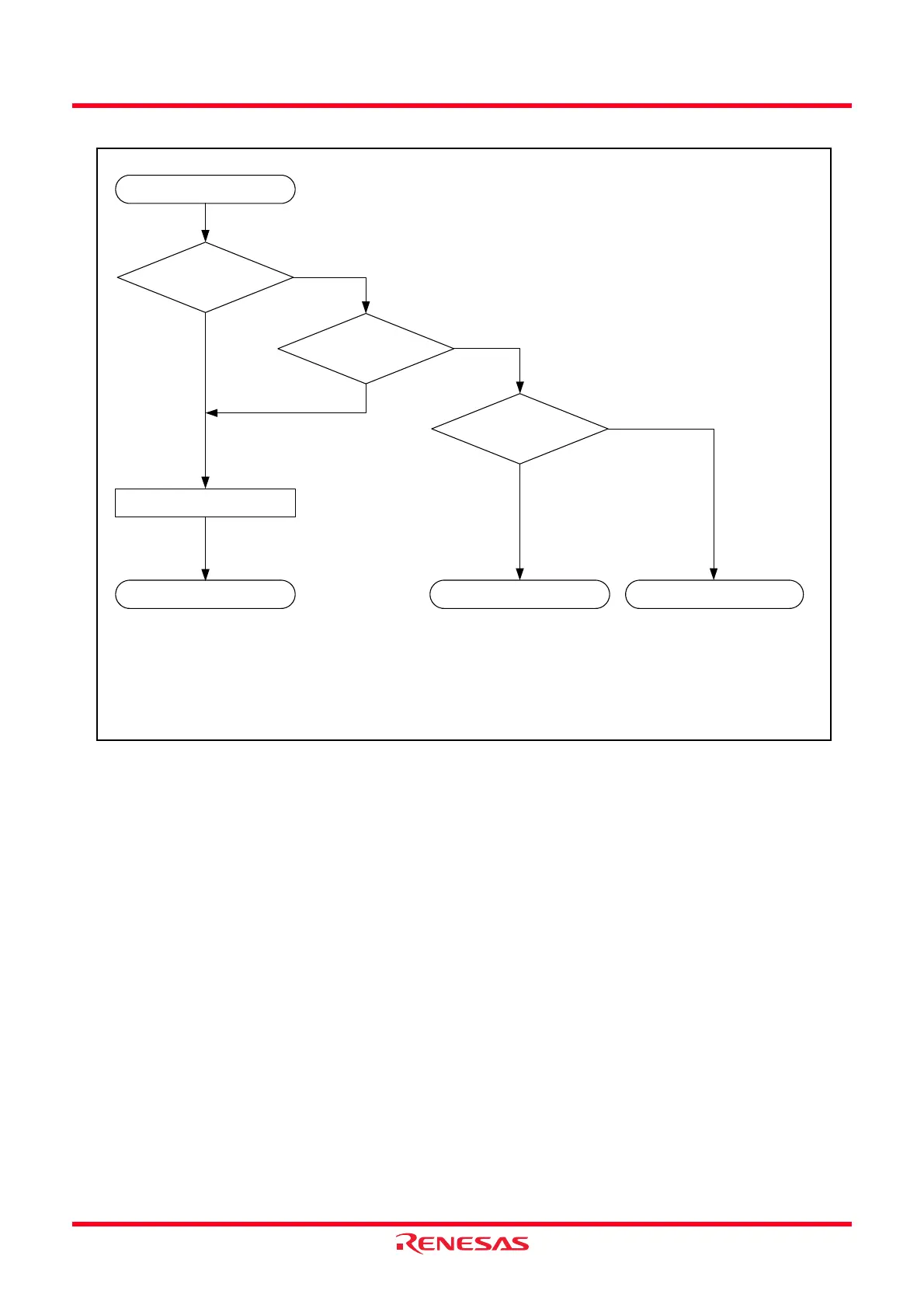

Figure 10.14 Example of Determining Interrupt Source for Oscillation Stop Detection, Watchdog

Timer, Voltage Monitor 1, or Voltage Monitor 2 Interrupt

NOTE:

1. This disables multiple oscillation stop detection interrupts.

OCD1 to OCD3: Bits in OCD register

VW2C3: Bit in VW2C register

Interrupt sources judgment

OCD3 = 1?

(XIN clock stops)

OCD1 = 1 (Oscillation

stop detection interrupt enable),

and OCD2=1 (Selects on-chip

oscillator clock)?

VW2C3 = 1?

(Watchdog time underflows)

Jump to oscillation stop detection

interrupt process routine.

Jump to voltage monitor 2 Interrupt

process routine.

Jump to watchdog timer interrupt

process routine.

NO

YES

NO

YES

NO

YES

OCD1 = 0 (Oscillation stop detection

interrupt disable)

(1)

Loading...

Loading...