R8C/20 Group, R8C/21 Group 5. Resets

Rev.2.00 Aug 27, 2008 Page 26 of 458

REJ09B0250-0200

5.2 Power-On Reset Function

(1)

When the RESET pin is connected to the VCC pin via a pull-up resistor, and the VCC pin voltage level rises, the

power-on reset function is enabled and the MCU resets its pins, CPU, and SFR. When a capacitor is connected to

the RESET

pin, too, always keep the voltage to the RESET pin 0.8VCC or more.

When the input voltage to the VCC pin reaches to the Vdet0 level or above, the low-speed on-chip oscillator clock

starts counting. When the low-speed on-chip oscillator clock count reaches 32, the internal reset signal is held “H”

and the MCU enters the reset sequence (refer to Figure 5.3). The low-speed on-chip oscillator clock divide-by-8 is

automatically selected for the CPU after reset.

Refer to 4. Special Function Registers (SFRs) for the status of the SFR after power-on reset.

The voltage monitor 0 reset is enabled after power-on reset.

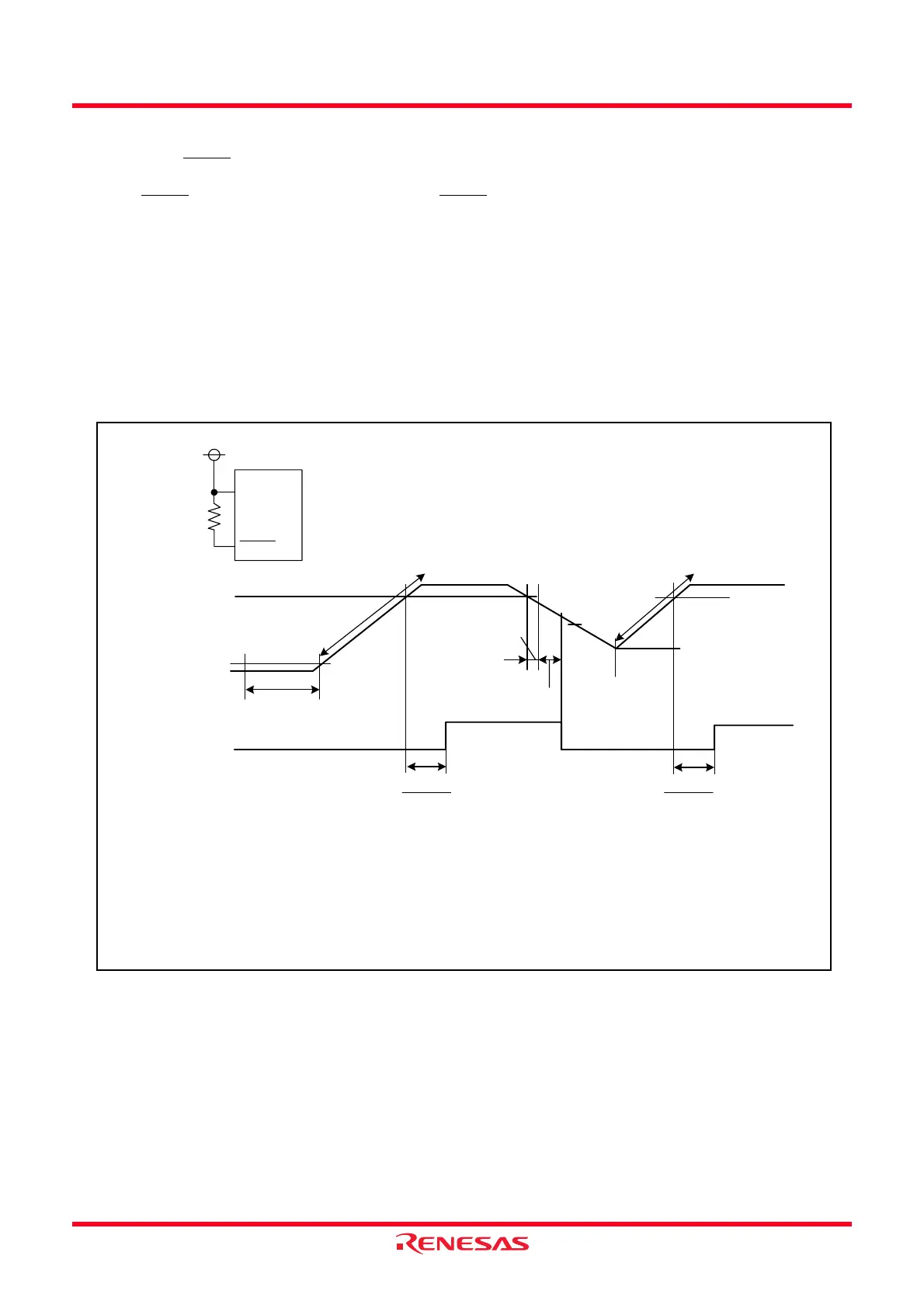

Figure 5.7 shows the Example of Power-On Reset Circuit and Operation.

NOTE:

1. When using power-on reset function, set the LVD1ON bit to 0 (voltage monitor 1 reset enabled after reset).

Figure 5.7 Example of Power-On Reset Circuit and Operation

× 32

1

fOCO-S

Vdet1

(3)

Vpor1

tw(por1)

Vdet1

(3)

Vpor2

2.0 V

trth

trth

External power Vcc

NOTES:

1. When using the voltage monitor 1 digital filter, ensure VCC is 2.0 V or higher during the sampling time.

2. The sampling clock can be selected. Refer to 6. Voltage Detection Circuit for details.

3. Vdet1 indicates the voltage detection level of the voltage detection 1 circuit. Refer to 6. Voltage Detection Circuit for details.

4. Refer to 20. Electrical Characteristics.

5. To use the power-on reset function, enable voltage monitor 1 reset by setting the LVD1ON bit in the OFS register to 0

(voltage monitor 1 reset enabled after reset), bits VW1C0 and VW1C6 in the VW1C register to 1 (enable) and the VCA26 bit

in the VCA2 register to 1 (voltage detection 1 circuit enabled).

Internal reset signal

(“L” valid)

Sampling time

(1, 2)

td(Vdet1-A)

× 32

1

fOCO-S

RESET

VCC

4.7 kΩ

(reference)

Loading...

Loading...