R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 283 of 458

REJ09B0250-0200

16.2 Clock Synchronous Serial I/O with Chip Select (SSU)

The serial data of the clock synchronous can communicate for the clock synchronous serial I/O with chip select.

Table 16.2 lists the Clock Synchronous Serial I/O with Chip Select Specifications and Figure 16.1 shows a Block

Diagram of Clock Synchronous Serial I/O with Chip Select.

Figures 16.2 to 16.9 show Clock Synchronous Serial I/O with Chip Select Associated Registers.

NOTE:

1. The interrupt vector table is one of the clock synchronous serial I/O with chip select specification.

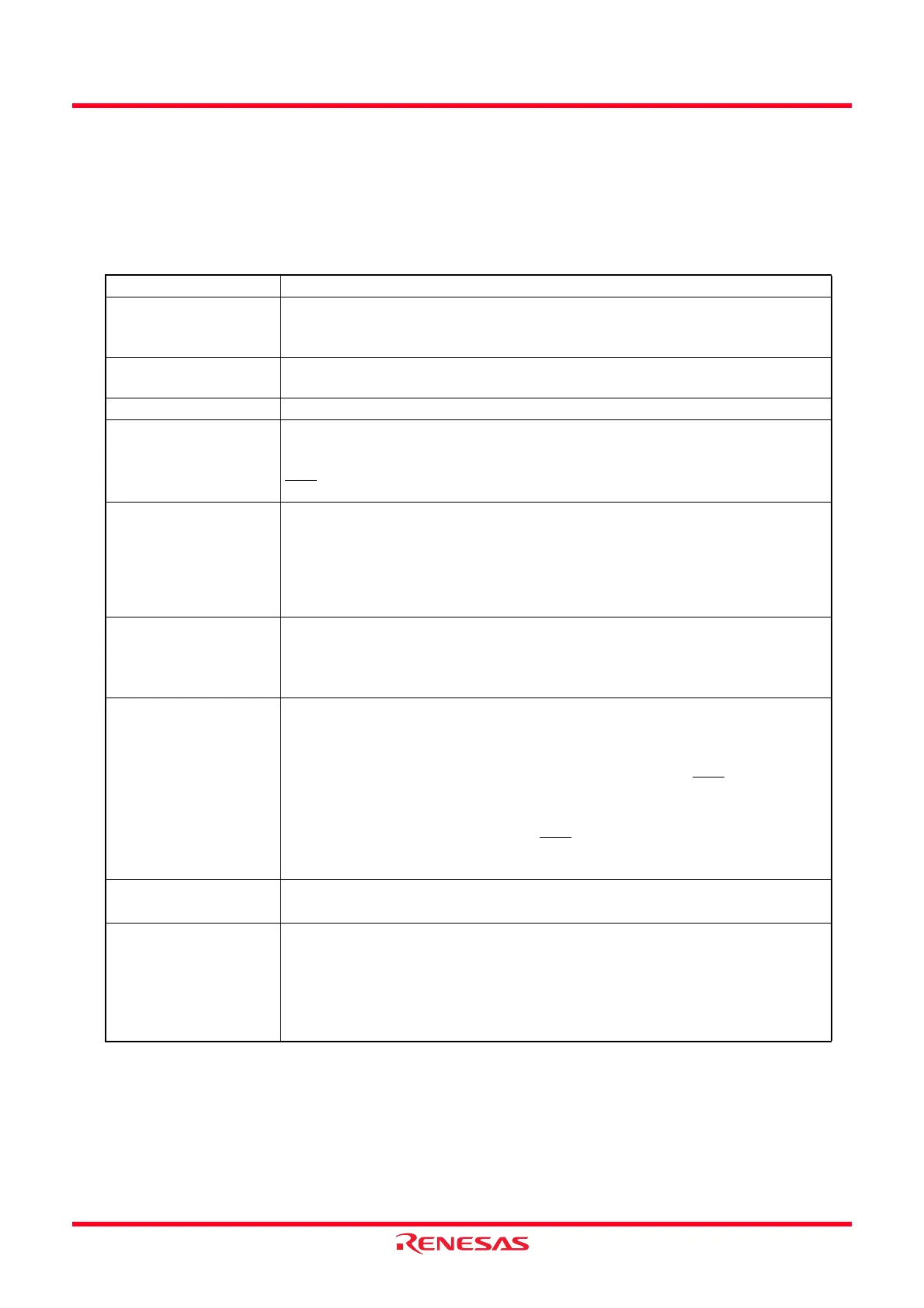

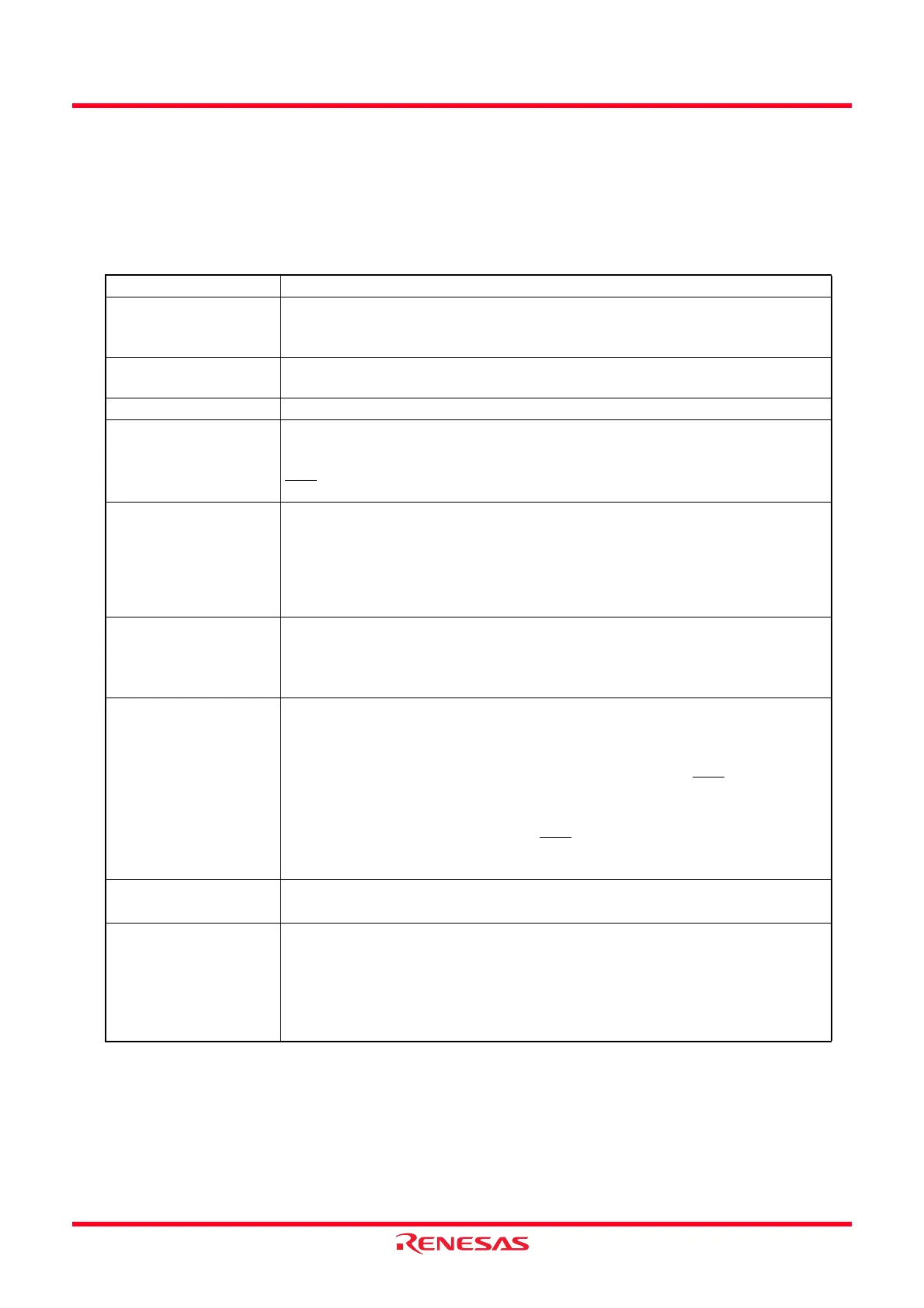

Table 16.2 Clock Synchronous Serial I/O with Chip Select Specifications

Item Specification

Transfer Data Format • Transfer-data length 8 bits

Continuous transmit and receive of serial data are enabled since both

transmitter and receiver have buffer structure.

Operating Mode • Clock synchronous communication mode

• 4-wire bus communication mode (including bidirectional communication)

Master / Slave Device Selectable

I/O Pin SSCK (I/O): Clock I/O pin

SSI (I/O): Data I/O pin

SSO (I/O): Data I/O pin

SCS

(I/O): Chip-select I/O pin

Transfer Clock • When the MSS bit in the SSCRH register is set to 0 (operates as slave

device), external clock can be selected.

• When the MSS bit in the SSCRH register is set to 1 (operates as master

device), internal clock (selects from f1/256, f1/128, f1/64, f1/32, f1/16, f1/8 and

f1/4 and outputs from SSCK pin) can be selected.

• Clock polarity and phase of SSCK can be selected.

Receive Error Detection • Overrun error

Overrun error occurs during receive and completes by error. While the RDRF

bit in the SSSR register is set to 1 (data in the SSRDR register) and

completing the next serial data receive, the ORER bit is set to 1.

Multimaster Error

Detection

• Conflict error

While the SSUMS bit in the SSMR2 register is set to 1 (4-wire bus

communication mode) and the MSS bit in the SSCRH register is set to 1

(operates as master device) and when starting a serial communication, the

CE bit in the SSSR register is set to 1 if “L” applies to the SCS

pin input.

When the SSUMS bit in the SSMR2 register is set to 1 (4-wire bus

communication mode), the MSS bit in the SSCRH register is set to 0

(operates as slave device) and the SCS

pin input changes state from “L” to

“H”, the CE bit in the SSSR register is set to 1.

Interrupt Request 5 interrupt requests (transmit-end, transmit-data-empty, receive-data-full,

overrun error and conflict error).

(1)

Select Function • Data transfer direction

Selects MSB-first or LSB-first

• SSCK clock polarity

Selects “L” or “H” level when clock stops

• SSCK clock phase

Selects edge of data change and data download

Loading...

Loading...