R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 284 of 458

REJ09B0250-0200

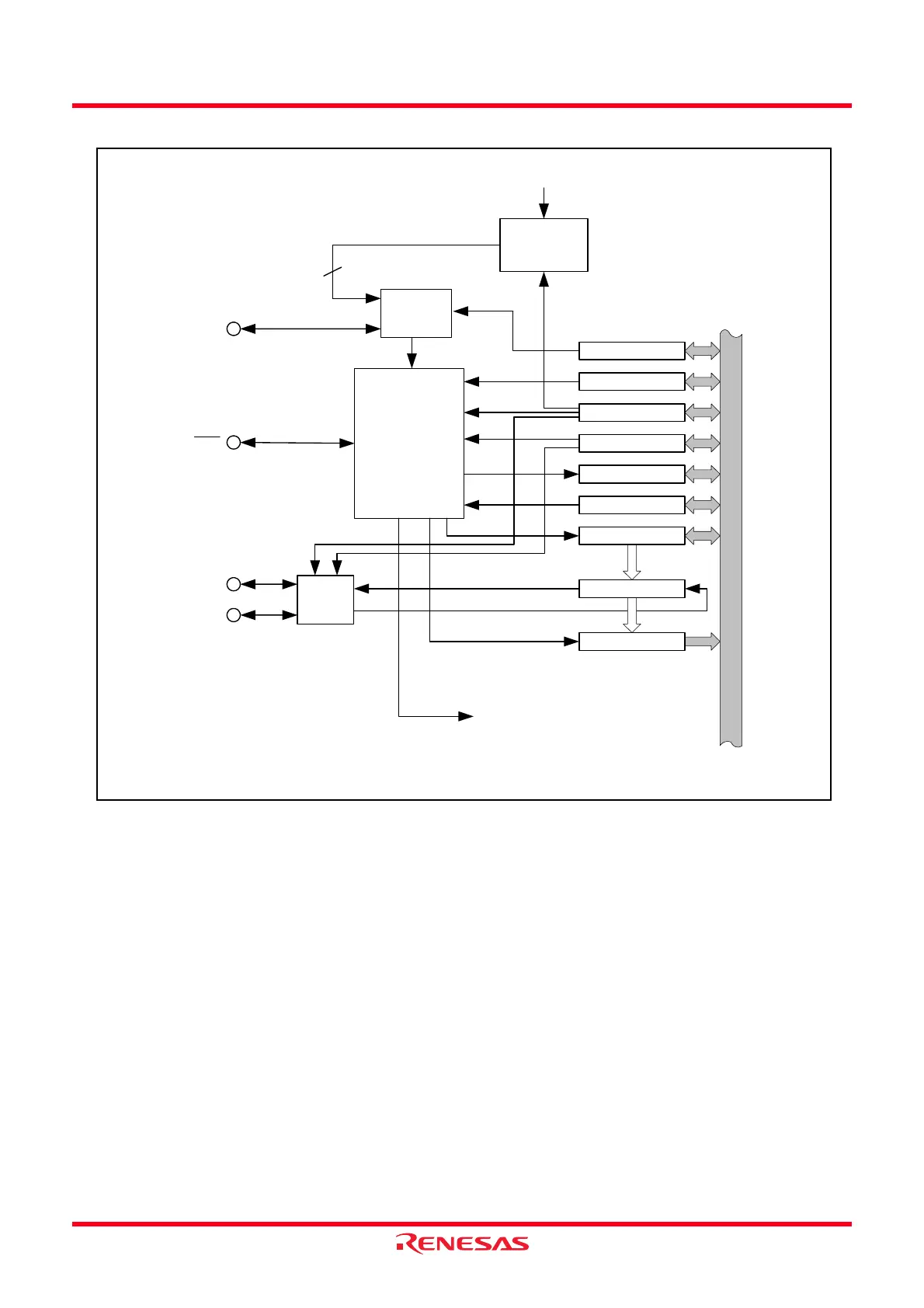

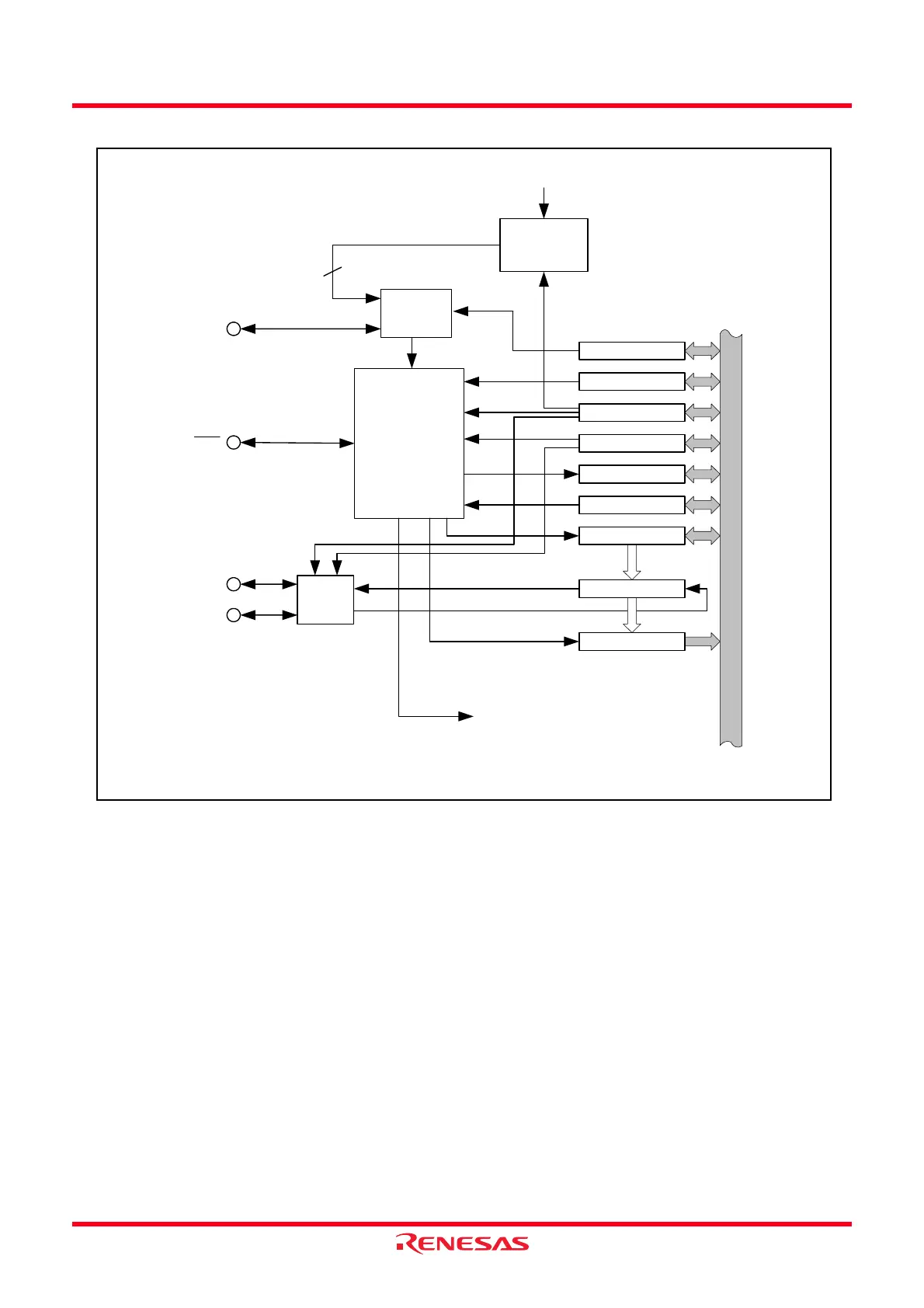

Figure 16.1 Block Diagram of Clock Synchronous Serial I/O with Chip Select

SSMR register

Data bus

Transmit/receive

control circuit

SSCRL register

SSCRH register

SSER register

SSSR register

SSMR2 register

SSTDR register

SSRDR register

Selector

Multiplexer

SSO

SSI

SCS

SSCK

Interrupt requests

(TXI, TEI, RXI, OEI and CEI)

Internal clock

generation

circuit

f1

Internal clock(f1/i)

i = 4, 8, 16, 32, 64, 128 and 256

SSTRSR register

Loading...

Loading...