R8C/20 Group, R8C/21 Group 15. Serial Interface

Rev.2.00 Aug 27, 2008 Page 271 of 458

REJ09B0250-0200

15.1 Clock Synchronous Serial I/O Mode

The clock synchronous serial I/O mode is mode to transmit and receive data using a transfer clock. This mode is

selected in UART0 only.

Table 15.1 lists the Clock Synchronous Serial I/O Mode Specifications. Table 15.2 lists the Registers Used and

Settings in Clock Synchronous Serial I/O Mode

(1)

.

NOTES:

1. When an external clock is selected, meet the conditions while the CKPOL bit in the U0C0 register is

set to 0 (transmit data output at the falling edge and the receive data input at the rising edge of the

transfer clock), the external clock is held “H”; if the CKPOL bit in the U0C0 register is set to 1

(transmit data output at the rising edge and the receive data input at the falling edge of the transfer

clock), the external clock is held “L”.

2. If an overrun error occurs, the receive data (b0 to b8) of the U0RB register will be undefined. The IR

bit in the S0RIC register remains unchanged.

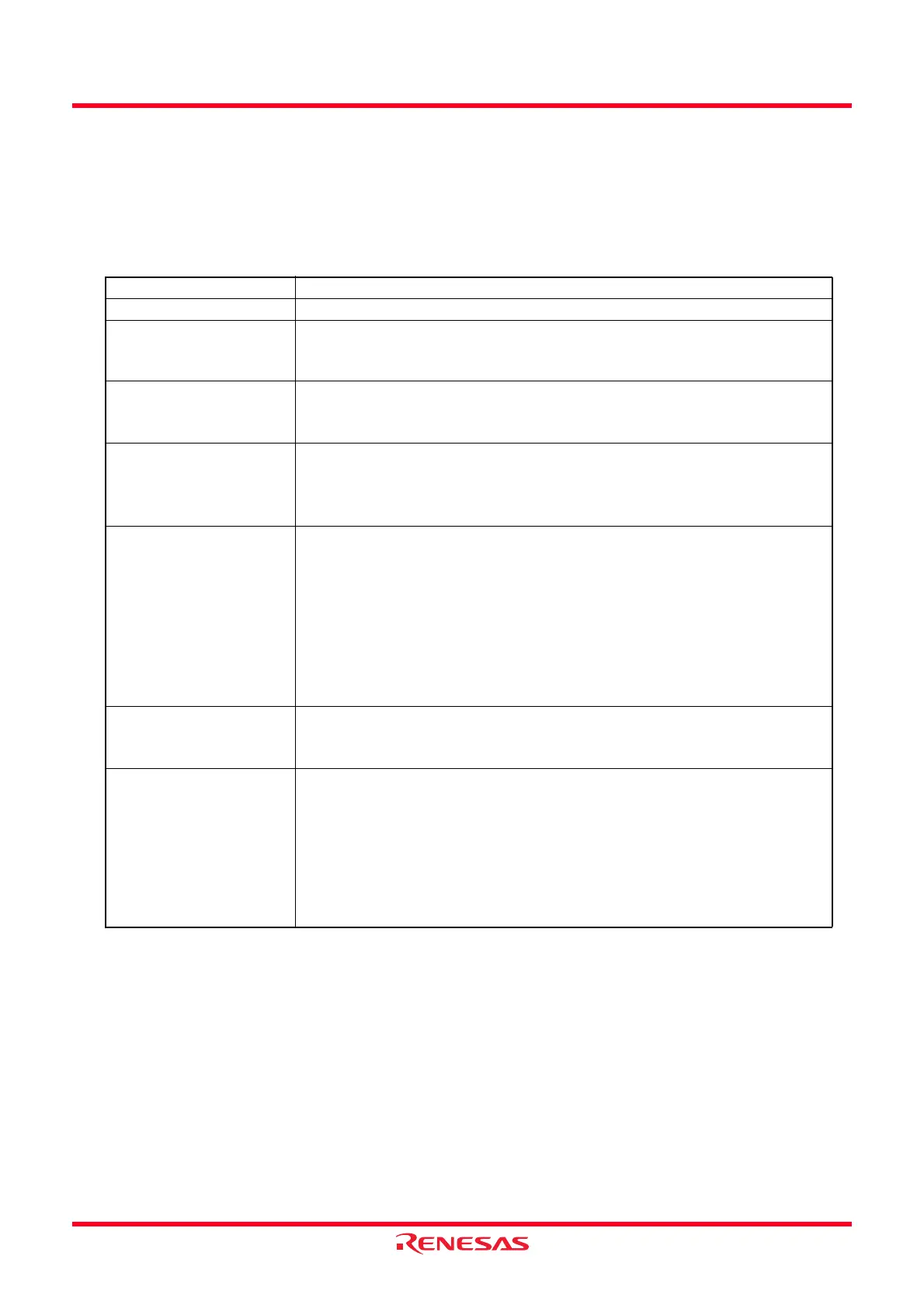

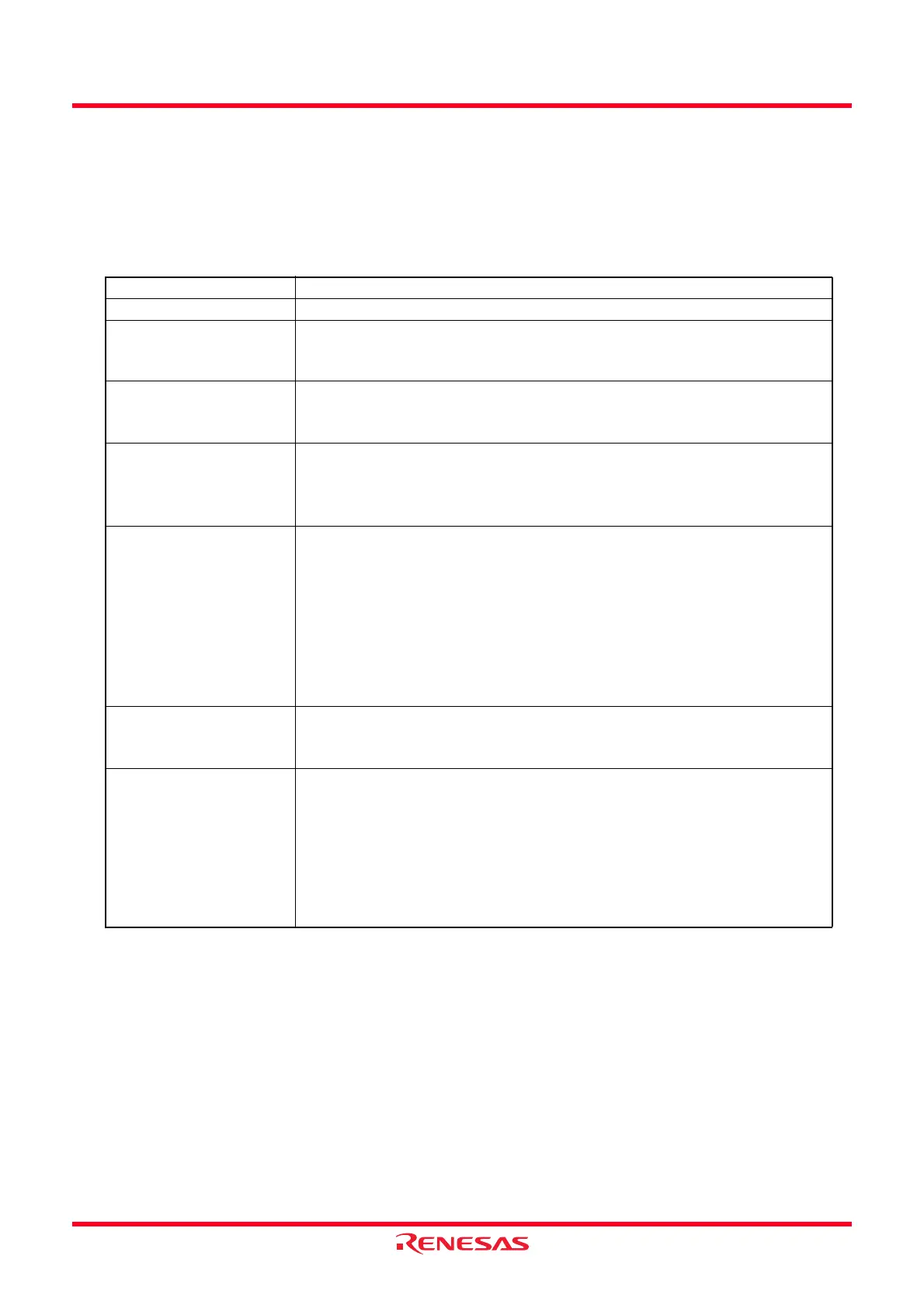

Table 15.1 Clock Synchronous Serial I/O Mode Specifications

Item Specification

Transfer Data Format • Transfer data length: 8 bits

Transfer Clocks • CKDIR bit in U0MR register is set to 0 (internal clock): fi/(2(n + 1))

fi = f1, f8, f32 n = setting value in U0BRG register: 00h to FFh

• The CKDIR bit is set to 1 (external clock): input from CLK0 pin

Transmit Start Conditions

• Before transmit starts, the following requirements are required

(1)

- The TE bit in the U0C1 register is set to 1 (transmit enabled)

- The TI bit in the U0C1 register is set to 0 (data in the U0TB register)

Receive Start Conditions

• Before receive starts, the following requirements are required

(1)

- The RE bit in the U0C1 register is set to 1 (receive enabled)

- The TE bit in the U0C1 register is set to 1 (transmit enabled)

- The TI bit in the U0C1 register is set to 0 (data in the U0TB register)

Interrupt Request

Generation Timing

• When transmit, one of the following conditions can be selected

- The U0IRS bit is set to 0 (transmit buffer empty):

when transferring data from the U0TB register to UART0 transmit register

(when transmit starts)

- The U0IRS bit is set to 1 (transmit completes):

when completing transmit data from UARTi transmit register

• When receive

When transferring data from the UART0 receive register to the U0RB

register (when receive completes)

Error Detection

• Overrun error

(2)

This error occurs if serial interface starts receiving the following data before

reading the U0RB register and receives the 7th bit of the following data

Select Functions • CLK polarity selection

Transfer data input/output can be selected to occur synchronously with the

rising or the falling edge of the transfer clock

• LSB first, MSB first selection

Whether transmitting or receiving data beginning with the bit 0 or beginning

with the bit 7 can be selected

• Continuous receive mode selection

Receive is enabled immediately by reading the U0RB register

Loading...

Loading...