R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 339 of 458

REJ09B0250-0200

16.3.6 Bit Synchronization Circuit

When setting the I

2

C bus interface in master mode.

• When the SCL signal is driven to “L” by the slave device.

• Since the “H” period may become shorter while the SCL signal is driven to “L” by the slave device and the

rising speed of the SCL signal is lowered by the load (load capacity and pull-up resistor) of the SCL line,

the SCL signal is monitored and the communication synchronizes per bit.

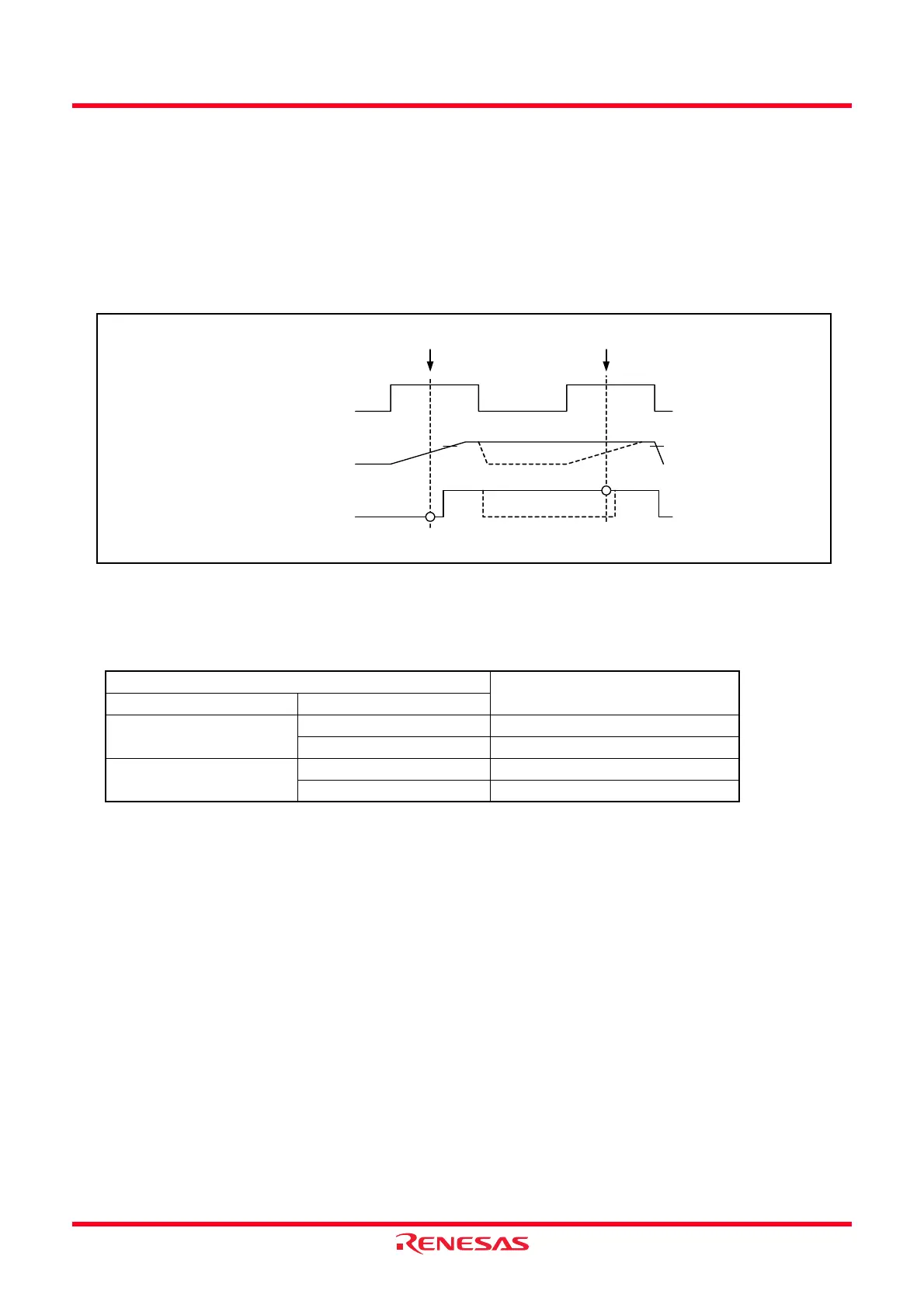

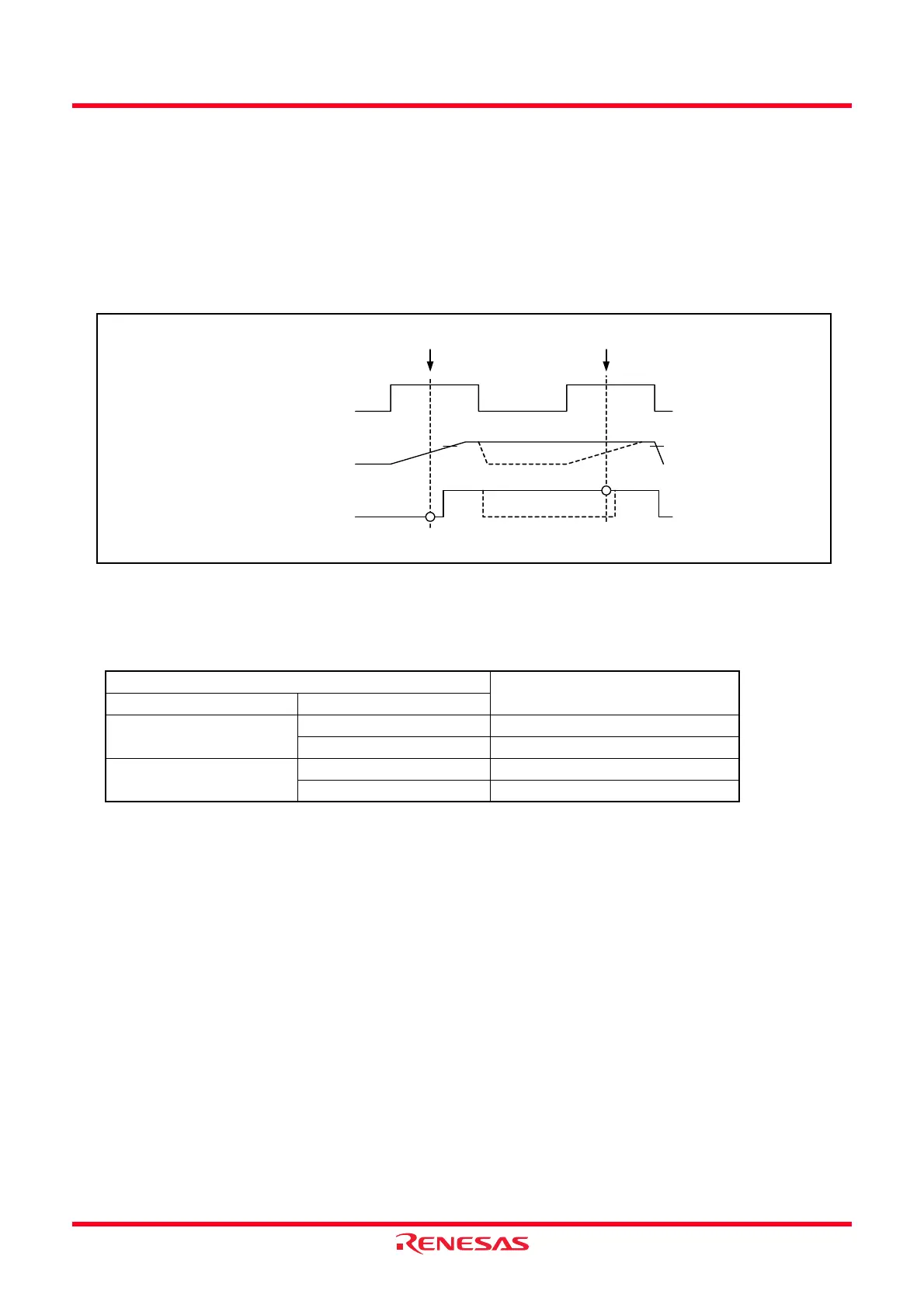

Figure 16.45 shows the Timing of Bit Synchronous Circuit and Table 16.8 lists the Time between Changing

SCL Signal from “L” Output to High-Impedance and Monitoring of SCL Signal.

Figure 16.45 Timing of Bit Synchronous Circuit

1 Tcyc = 1/f1(s)

Table 16.8 Time between Changing SCL Signal from “L” Output to High-Impedance and

Monitoring of SCL Signal

ICCR1 Register

Time for Monitoring SCL

CKS3 CKS2

0 0 7.5 Tcyc

1 19.5 Tcyc

1 0 17.5 Tcyc

1 41.5 Tcyc

VIH

Basis clock of SCL

monitor timing

SCL

Internal SCL

Loading...

Loading...