R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 297 of 458

REJ09B0250-0200

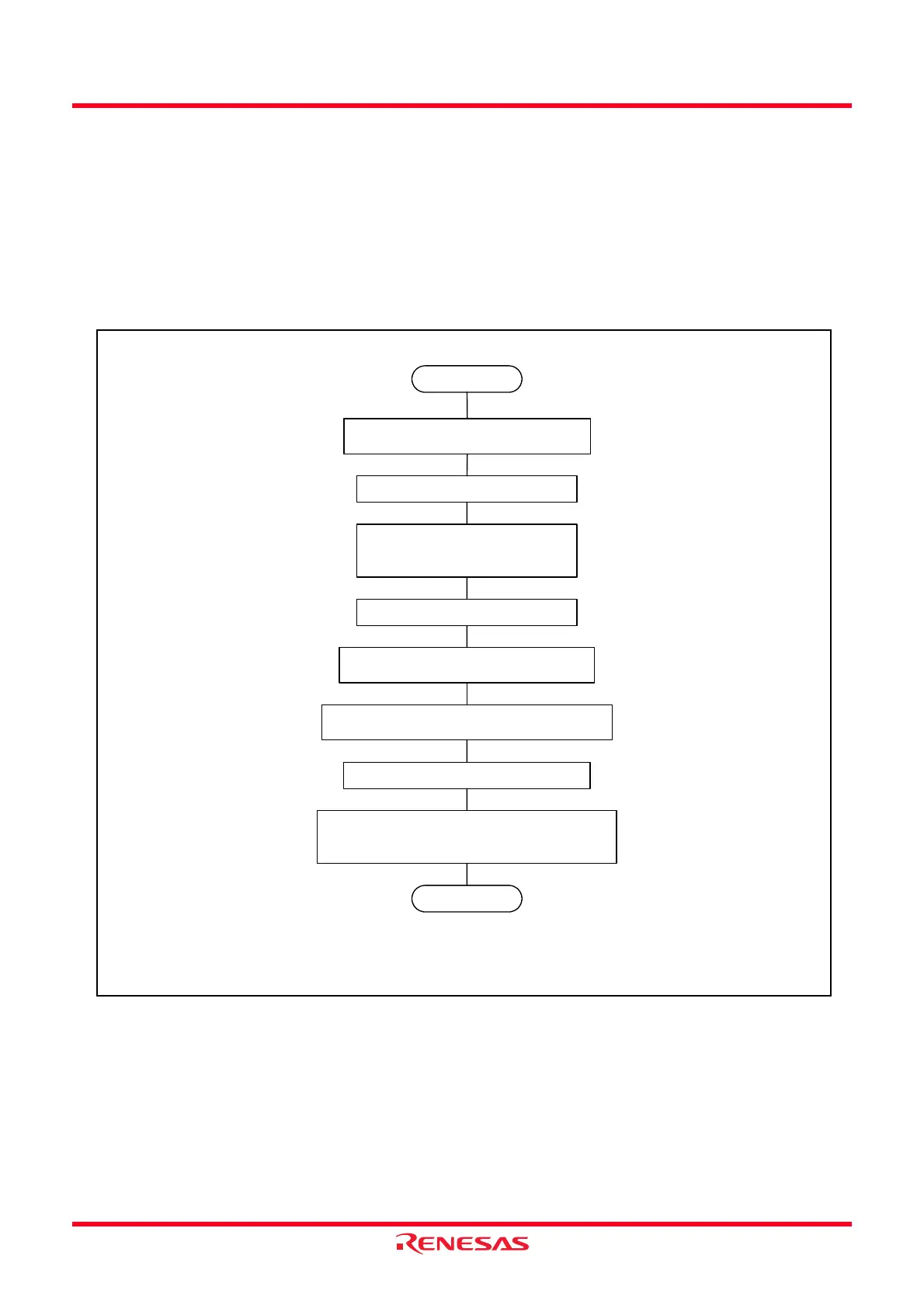

16.2.5 Clock Synchronous Communication Mode

16.2.5.1 Initialization in Clock Synchronous Communication Mode

Figure 16.12 shows an Initialization in Clock Synchronous Communication Mode. Set the TE bit in the SSER

register to 0 (disables transmit) and the RE bit to 0 (disables receive) before data transmit / receive as an

initialization.

When communication mode and format are changed, set the TE bit to 0 and the RE bit to 0 before changing.

Setting the RE bit to 0 does not change the contents of the RDRF and ORER flags, and the contents of the

SSRDR register.

Figure 16.12 Initialization in Clock Synchronous Communication Mode

Start

SSMR2 register SSUMS bit ← 0

SSCRH register Set CKS0 to CKS2 bits

Set RSSTP bit

SSSR register ORER bit ← 0

(1)

SSER register RE bit ← 1 (When receive)

TE bit

← 1 (When transmit)

Set RIE, TEIE and TIE bits

End

NOTE:

1. Write 0 after reading 1 to set the ORER bit to 0.

SSER register RE bit ← 0

TE bit

← 0

SSMR2 register SCKS bit ← 1

Set SOOS bit

SSCRH register Set MSS bit

SSMR register CPHS bit ← 0

CPOS bit

← 0

Set MLS bit

Loading...

Loading...