R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 291 of 458

REJ09B0250-0200

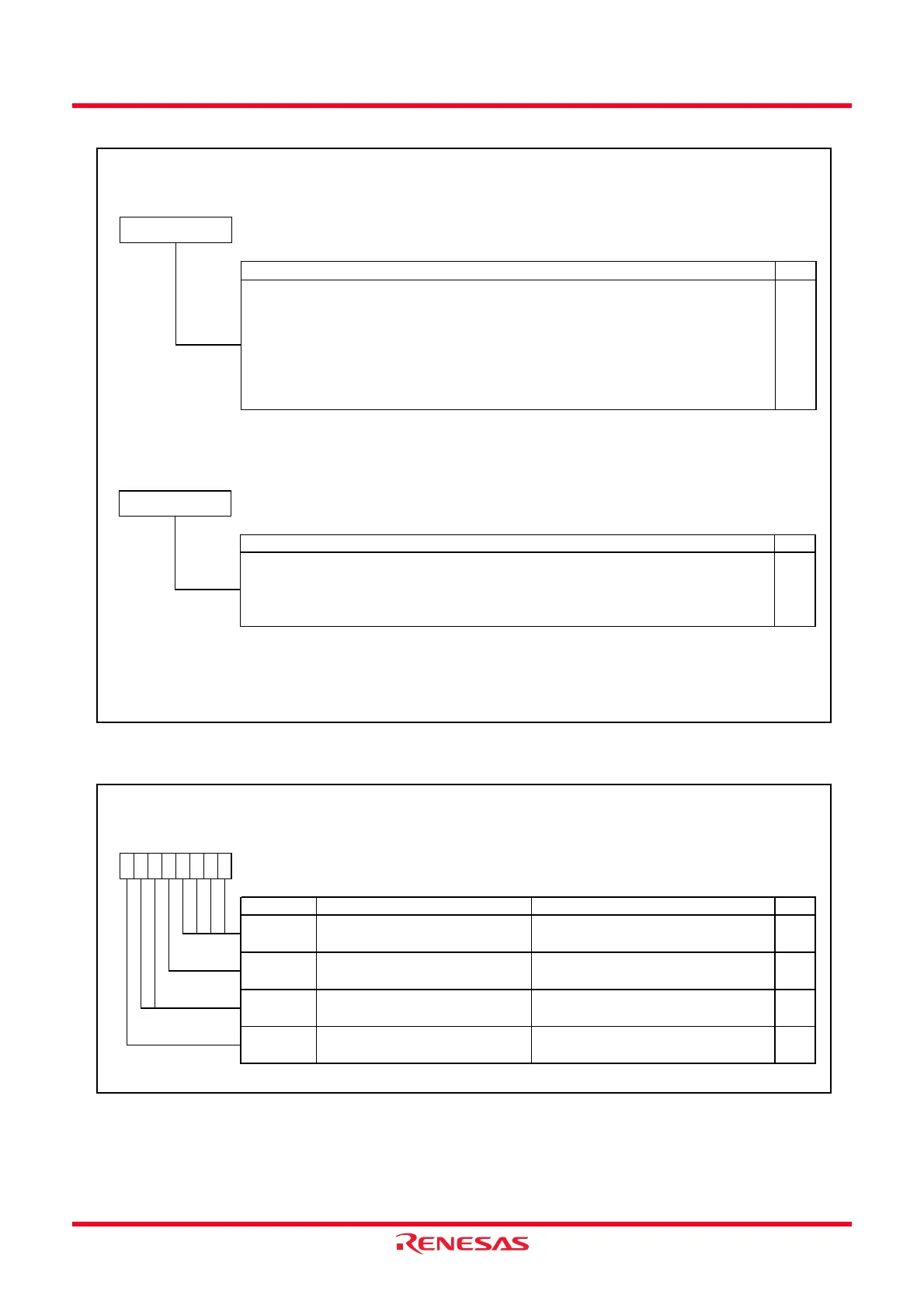

Figure 16.8 Registers SSTDR and SSRDR

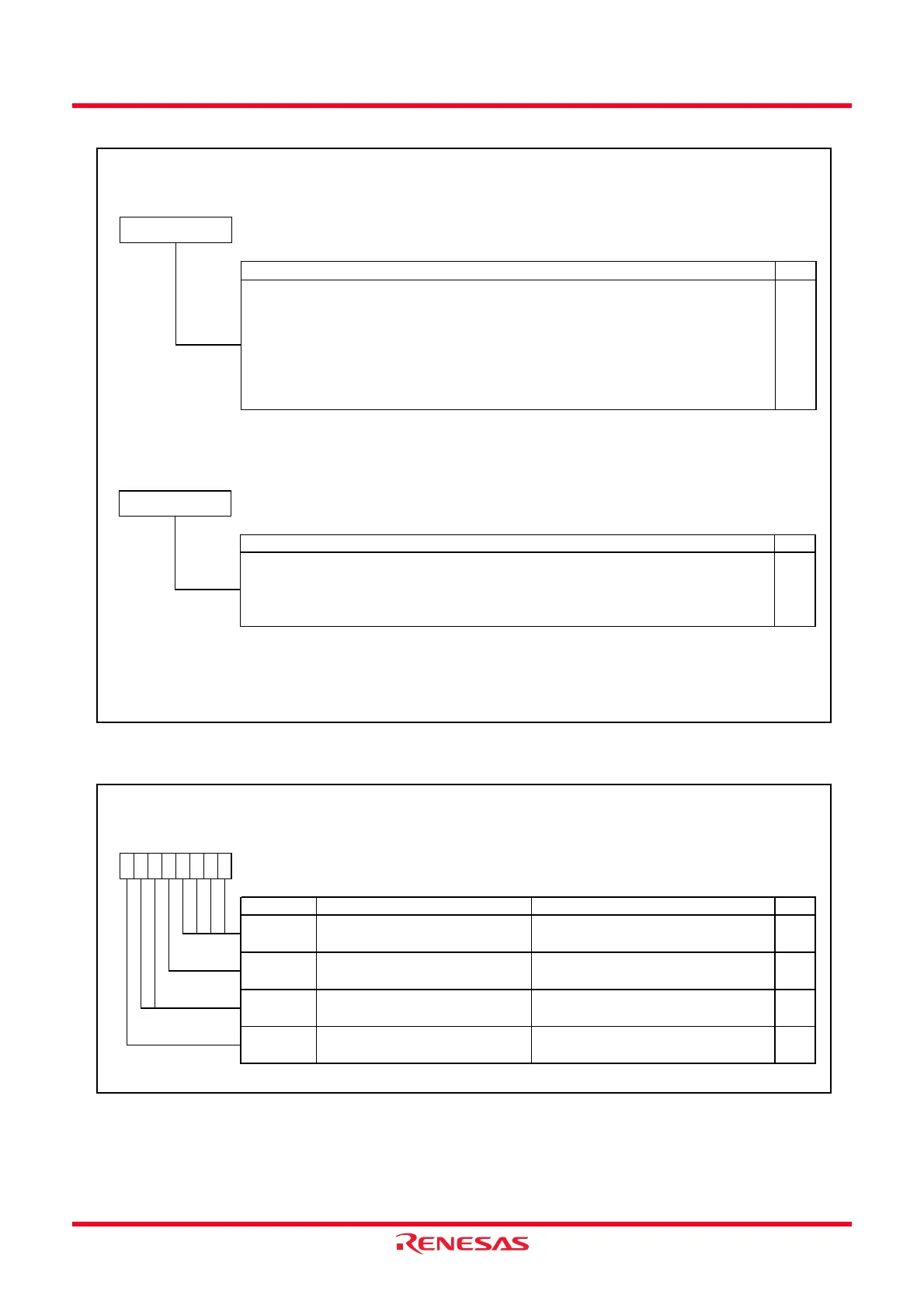

Figure 16.9 PMR Register

SS Transmit Data Register

Symbol Address After Reset

SSTDR

00BEh FFh

RW

RW

Function

Store the transmit data.

The stored transmit data is transferred to the SSTRSR register and the transmit is started

w hen detecting the SSTRSR register is empty.

When the next transmit data is w ritten to the SSTDR register during the data transmit from the

SSTRSR register, the data can be transmitted continuously.

(1)

When the MLS bit in the SSMR register is set to 1 (transfer data w ith LSB-first), the data in

w hich MSB and LSB are reversed can be read, after w riting to the SSTDR register.

b0b7

SS Receive Data Register

Symbol Address After Reset

SSRDR

00BFh FFh

RW

NOTE:

1. The SSRDR register maintains the receive data before the overrun error occurs w hen the ORER bit in the SSSR

register is set to 1 (overrun error occurs). When an overrun error occurs, the receive data may contain errors and

therefore, should be discarded.

Store the receive data.

(1)

The receive data is transferred to the SSRDR register and the receive operation is completed

w hen receiving 1-byte data to the SSTRSR register. At this time, the follow ing receive is

possible. The continuous receive is possible by the SSTRSR and SSRDR registers.

RO

Function

b7 b0

Port Mode Registe

Symbol Address After Reset

PMR

00F8h 00h

Bit Symbol Bit Name Function RW

IICSEL RW

0 : SSU function selects

1 : I

2

C bus function selects

Set to 0

0 : I/O port P6_6, P6_7

1 : TXD1, RXD1

Set to 0

—

Reserved bits

SSU/I

2

C bus sw itch bit

RW

b0

0

—

Reserved bits

U1PINSEL

Port TXD1/RXD1 switch bit

—

(b3-b0)

—

(b6-b5)

b3 b2

0

b1

00

b7 b6 b5 b4

00

Loading...

Loading...