R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 293 of 458

REJ09B0250-0200

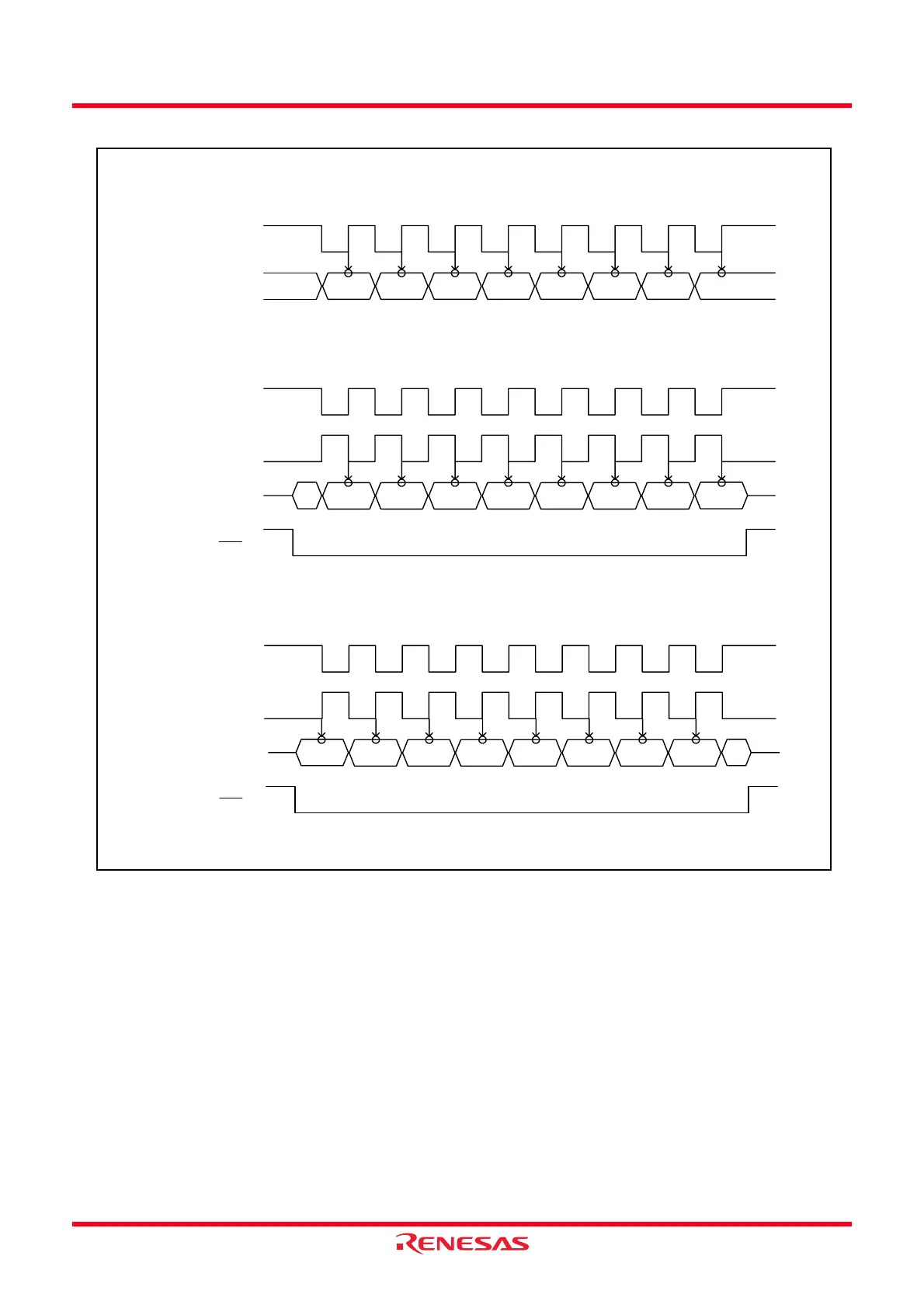

Figure 16.10 Association between Transfer Clock Polarity, Phase, and Transfer Data

SSCK

b0

SSO, SSI

• When SSUMS bit = 0 (clock synchronous communication mode), CPHS bit = 0 (data change at odd

edge) and CPOS bit = 0 (“H” when clock stops)

b1 b2 b3 b4 b5 b6 b7

SSCK

CPOS = 0

(“H” when clock stops)

b0SSO, SSI

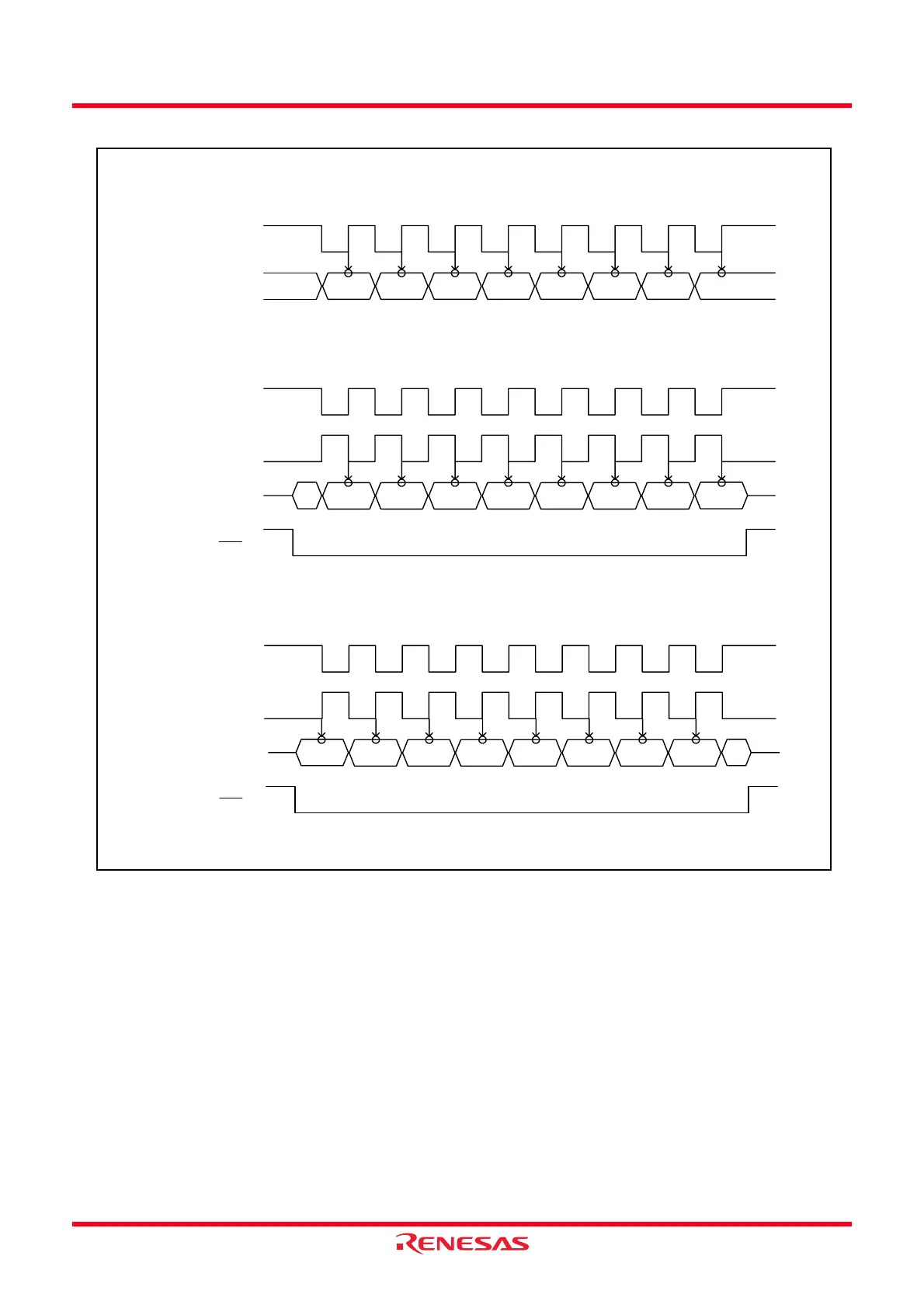

• When SSUMS bit = 1 (4-wire bus communication mode) and CPHS bit = 0 (data change at odd edge)

b1 b2 b3 b4 b5 b6 b7

SSCK

CPOS = 1

(“L” when clock stops)

SCS

SSCK

CPOS = 0

(“H” when clock stops)

SSO, SSI

• When SSUMS bit = 1 (4-wire bus communication mode), CPHS bit = 1 (data download at odd edge)

SSCK

CPOS = 1

(“L” when clock stops)

SCS

b0 b1 b2

b3 b4

b5

b6

b7

CPHS and CPOS: bits in SSMR register, SSUMS: Bits in SSMR2 register

Loading...

Loading...