R8C/20 Group, R8C/21 Group 21. Usage Notes

Rev.2.00 Aug 27, 2008 Page 439 of 458

REJ09B0250-0200

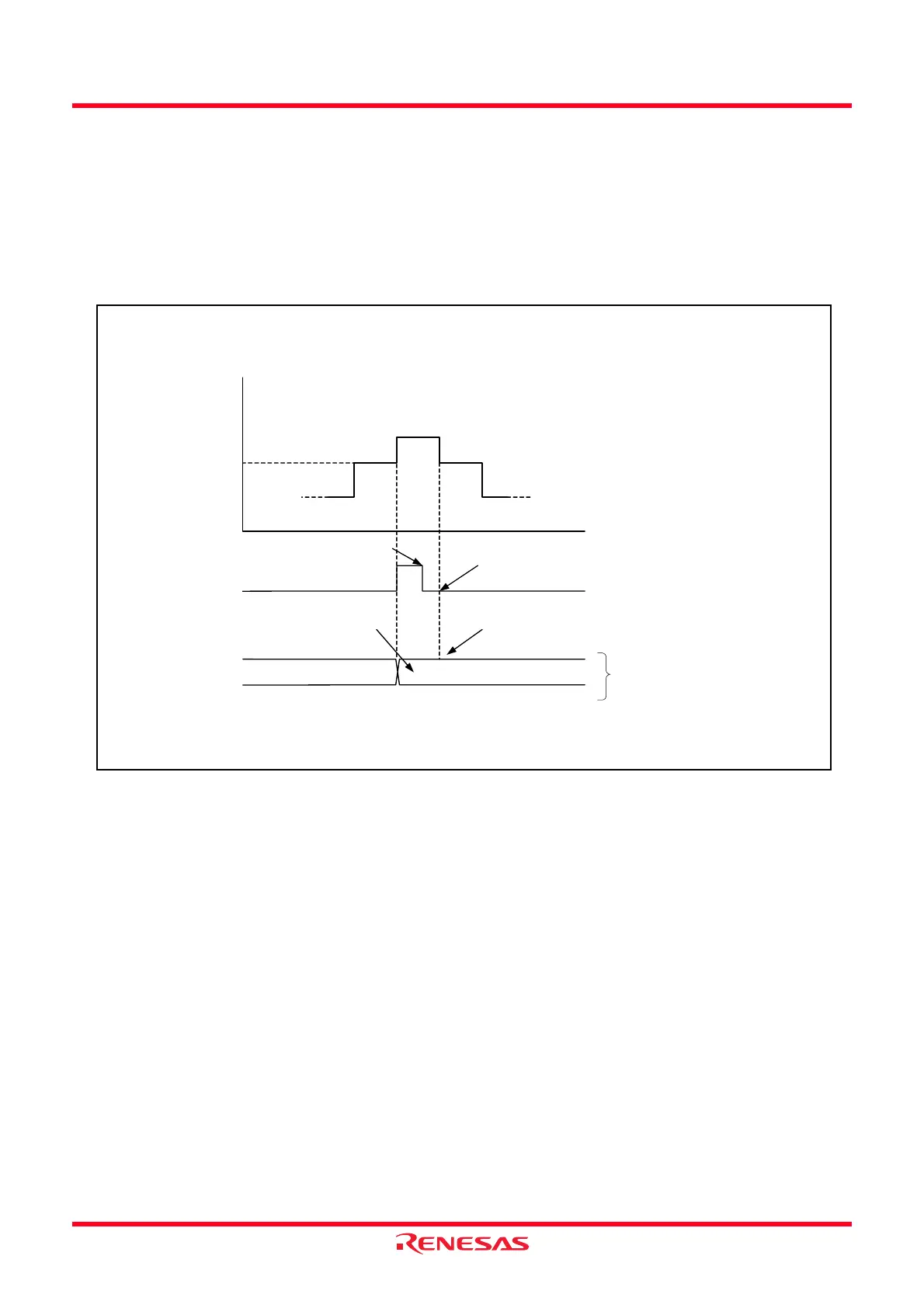

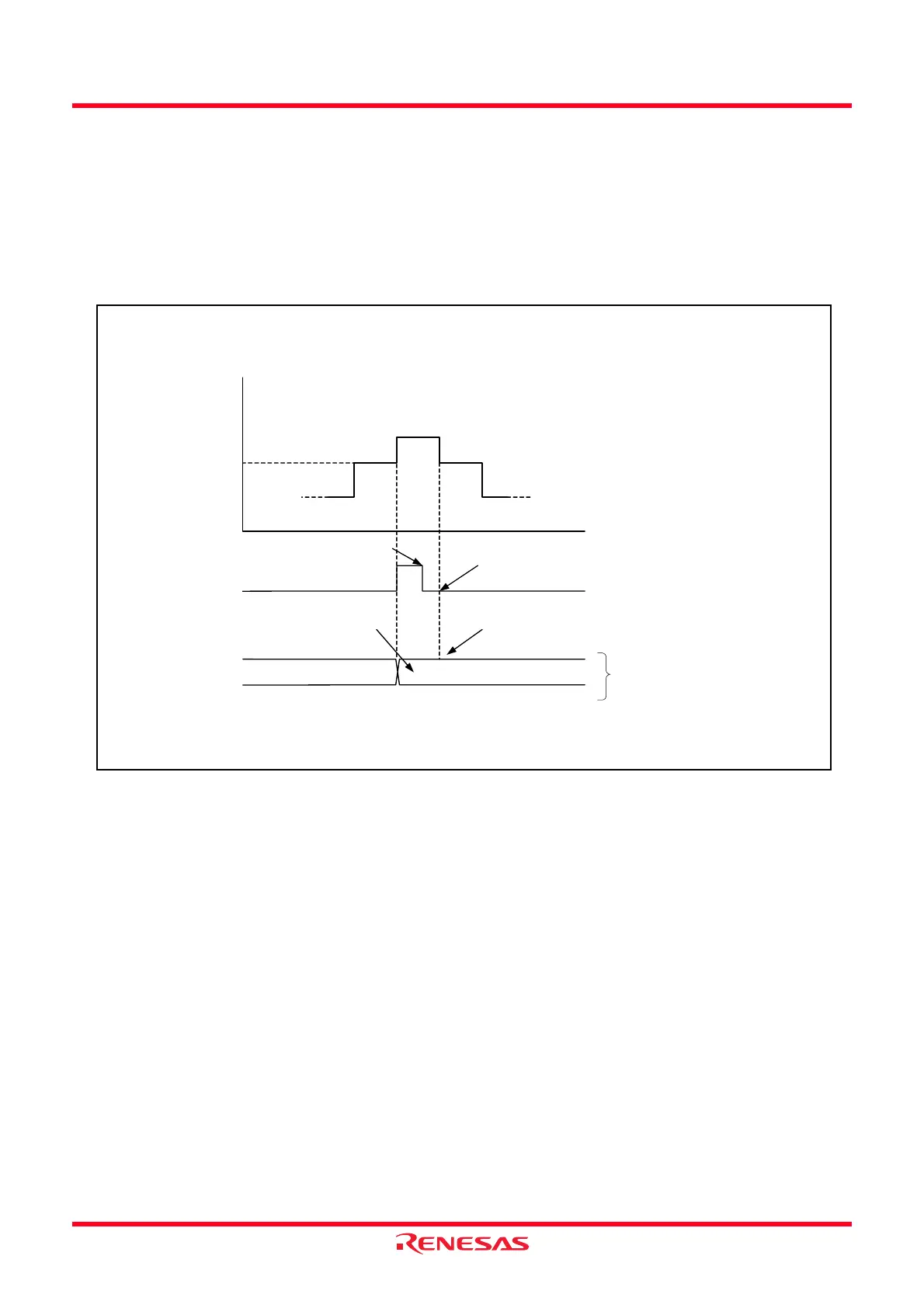

• When the value in the TRDGRA0 register is assumed as m, the TRD0 register counts order of m - 1, m, m

+ 1, m, m - 1 when changing from increment to decrement.

When changing from m to m + 1, the IMFA bit is set to 1. Also, the CMD1 to CMD0 bits in the TRDFCR

register are set to 11b (complementary PWM mode, buffer data transferred by the compare match in the

TRD0 and TRDGRA0 registers), the content in the buffer register (TRDGRD0, TRDGRC1, TRDGRD1) is

transferred to the general register (TRDGRB0, TRDGRA1, TRDGRB1).

For the order of m + 1, m, m - 1 operation, the IMFA bit remains unchanged and data are not transferred to

the register such as the TRDGRA0 register.

Figure 21.4 Operation at Compare Match between Registers TRD0 and TRDGRA0 in

Complementary PWM Mode

No change

IMFA bit in

TRDSR0 register

Transferred from

buffer register

TRDGRB0 register

TRDGRA1 register

TRDGRB1 register

Count value in TRD0

register

Setting value in

TRDGRA0

register m

m + 1

Set to 0 by a program

Not transferred from buffer register

When the CMD1 to CMD0 bits in the

TRDFCR register are set to 11b.

(Transfer from the buffer register to the

general register at the compare match

of the TRD0 register and TRDGRA0

register)

1

0

Loading...

Loading...