R8C/20 Group, R8C/21 Group 6. Voltage Detection Circuit

Rev.2.00 Aug 27, 2008 Page 32 of 458

REJ09B0250-0200

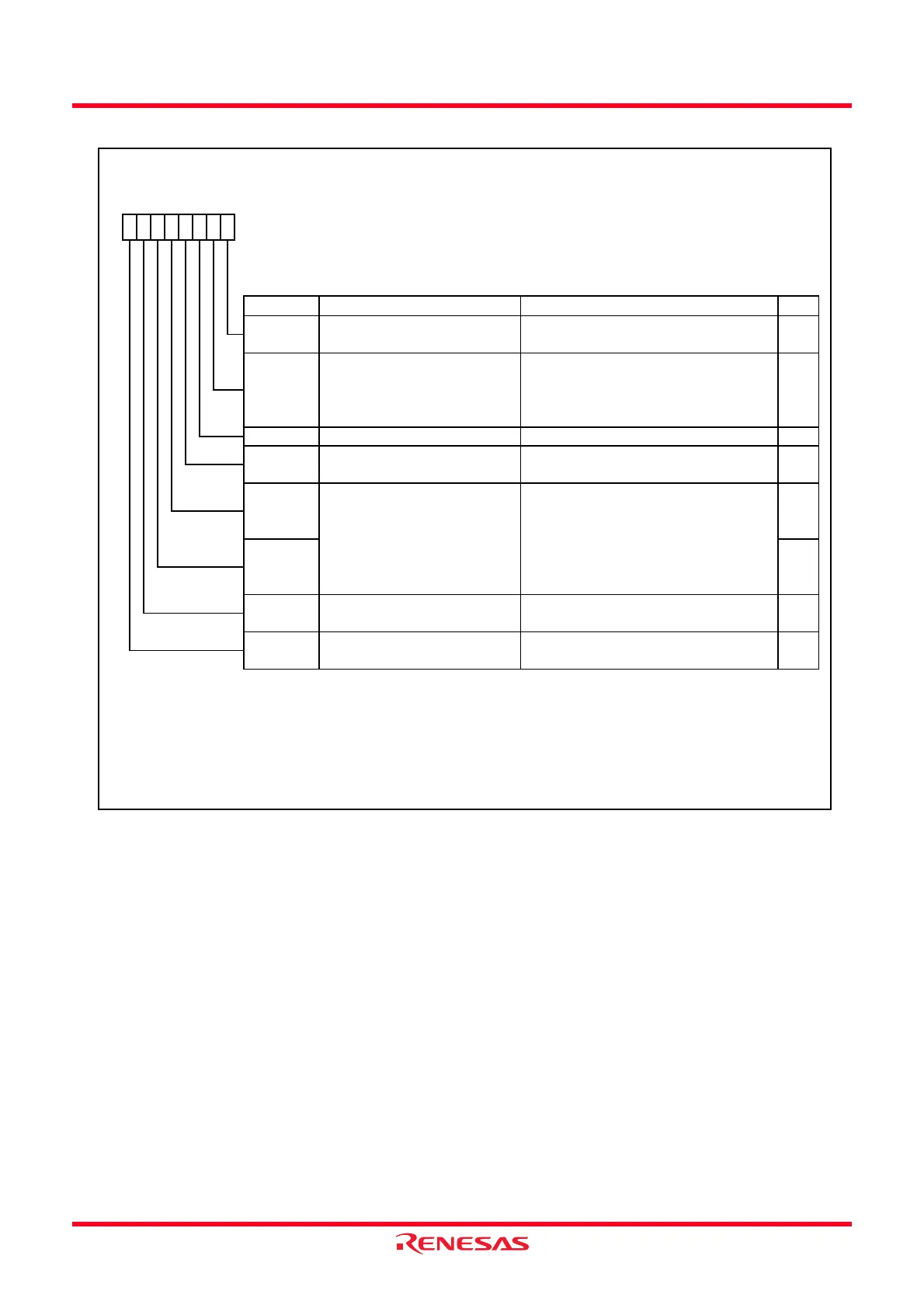

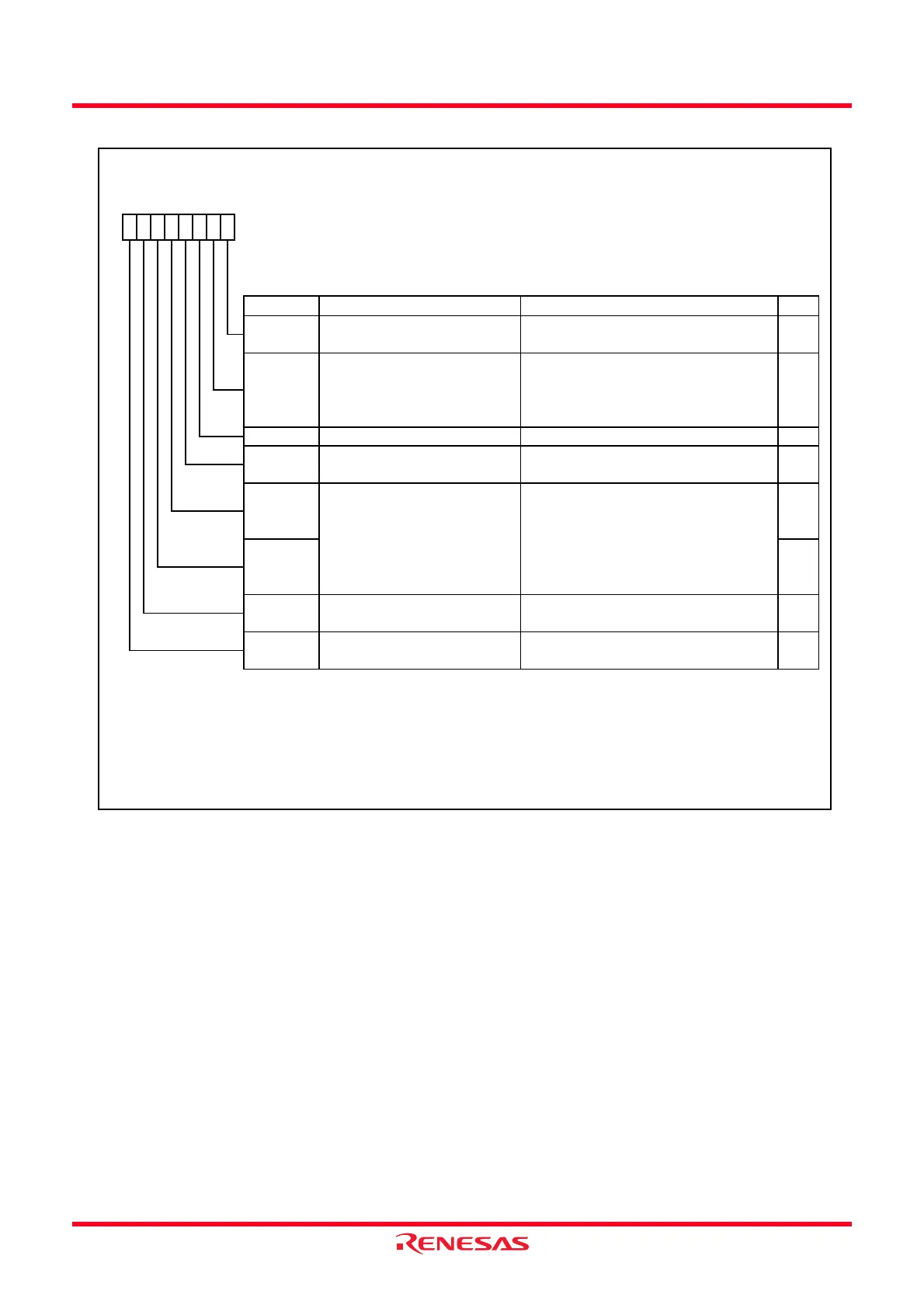

Figure 6.5 VW1C Register

Voltage Monitor 1 Circuit Control Register

(1)

Symbol Address

VW1C 0036h

Bit Symbol Bit Name Function RW

NOTES:

1.

2.

3.

4.

The LVD1ON bit in the OFS register is set to 1: 0000X000b

Power-on reset, voltage monitor 1 reset or the LVD1ON bit

in the OFS register is set to 0: 0100X001b

After Reset

(2)

b3 b2

0

VW1C0 RW

Voltage monitor 1 reset enable

bit

(3)

0 : Disable

1 : Enable

b1 b0b7 b6 b5 b4

0 : Digital filter enabled mode

(digital filter circuit enabled)

1 : Digital filter disabled mode

(digital filter circuit disabled)

RW

VW1C2 Reserved bit

VW1C1

Voltage monitor 1 digital filter

disable mode select bit

Set to 0 RW

—

(b3)

Reserved bit

VW1F1 RW

Sampling clock select bits

b5 b4

0 0 : fOCO-S divide-by-1

0 1 : fOCO-S divide-by-2

1 0 : fOCO-S divide-by-4

1 1 : fOCO-S divide-by-8

VW1F0 RW

When read, the content is undefined.

RO

VW1C6

Voltage monitor 1 circuit mode

select bit

When the VW1C0 bit is set to 1 (enables

voltage monitor 1 reset), set to 1.

RW

VW1C7

Voltage monitor 1 reset generation

condition select bit

(4)

When the VW1C1 bit is set to 1 (digital filter

disabled mode), set to 1.

RW

The VW1C7 bit is enabled w hen the VW1C1 bit is set to 1 (digital filter disabled mode).

Set the PRC3 bit in the PRCR register to 1 (w rite enable) before w riting to the VW1C register.

The value other than the VW1CO and VW1C6 bits remains unchanged after softw are reset, w atchdog timer reset,

and voltage monitor 2 reset.

The VW1C0 bit is enabled w hen the VCA26 bit in the VCA2 register is set to 1 (voltage detection 1 circuit

enabled). Set the VW1C0 bit to 0 (disable), w hen the VCA26 bit is set to 0 (voltage detection 1 circuit disabled).

Loading...

Loading...