RH850/F1K Series Hardware Design Guide

R01AN2911EJ0100 Rev. 1.00 Page 35 of 46

Aug 04, 2016

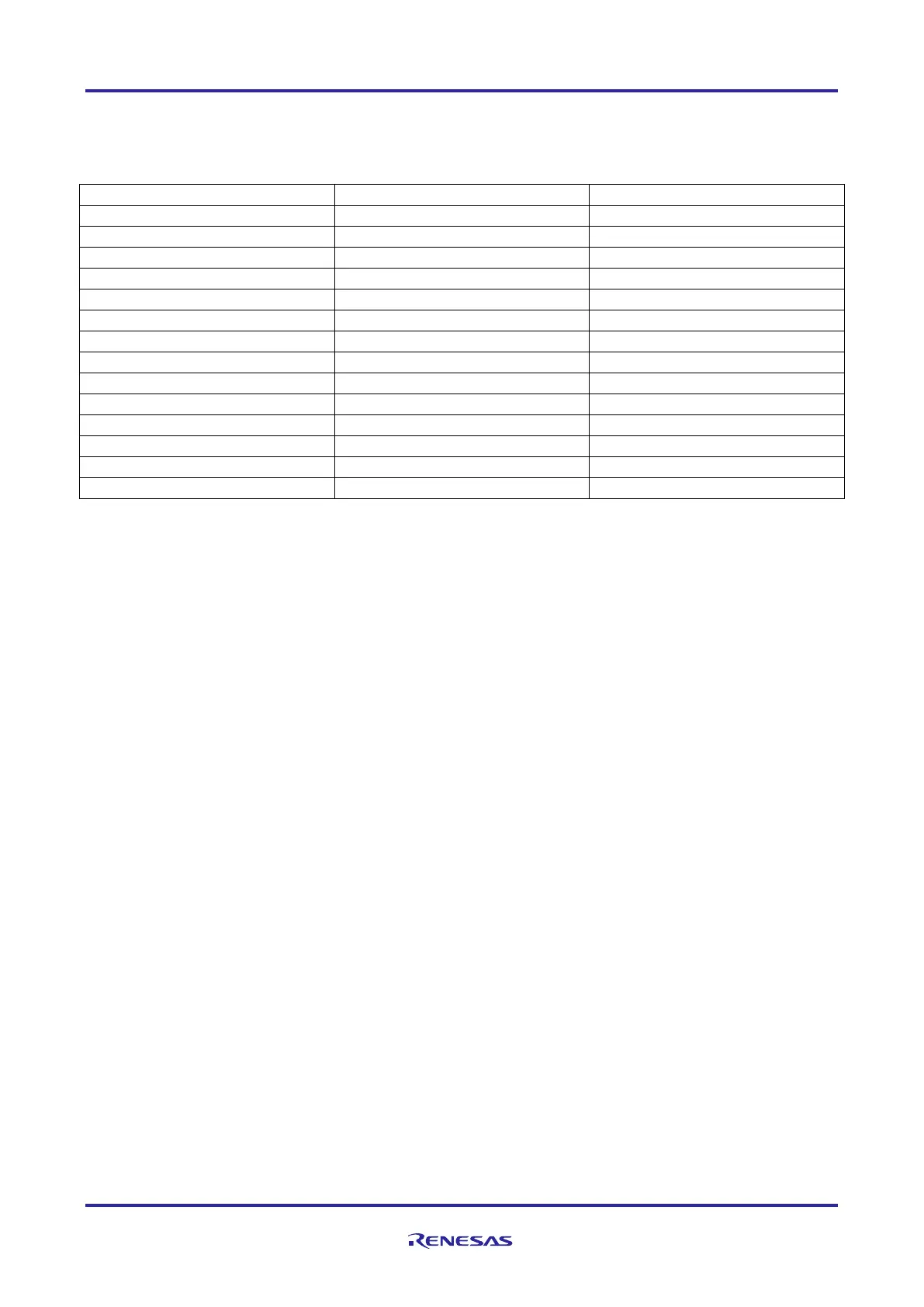

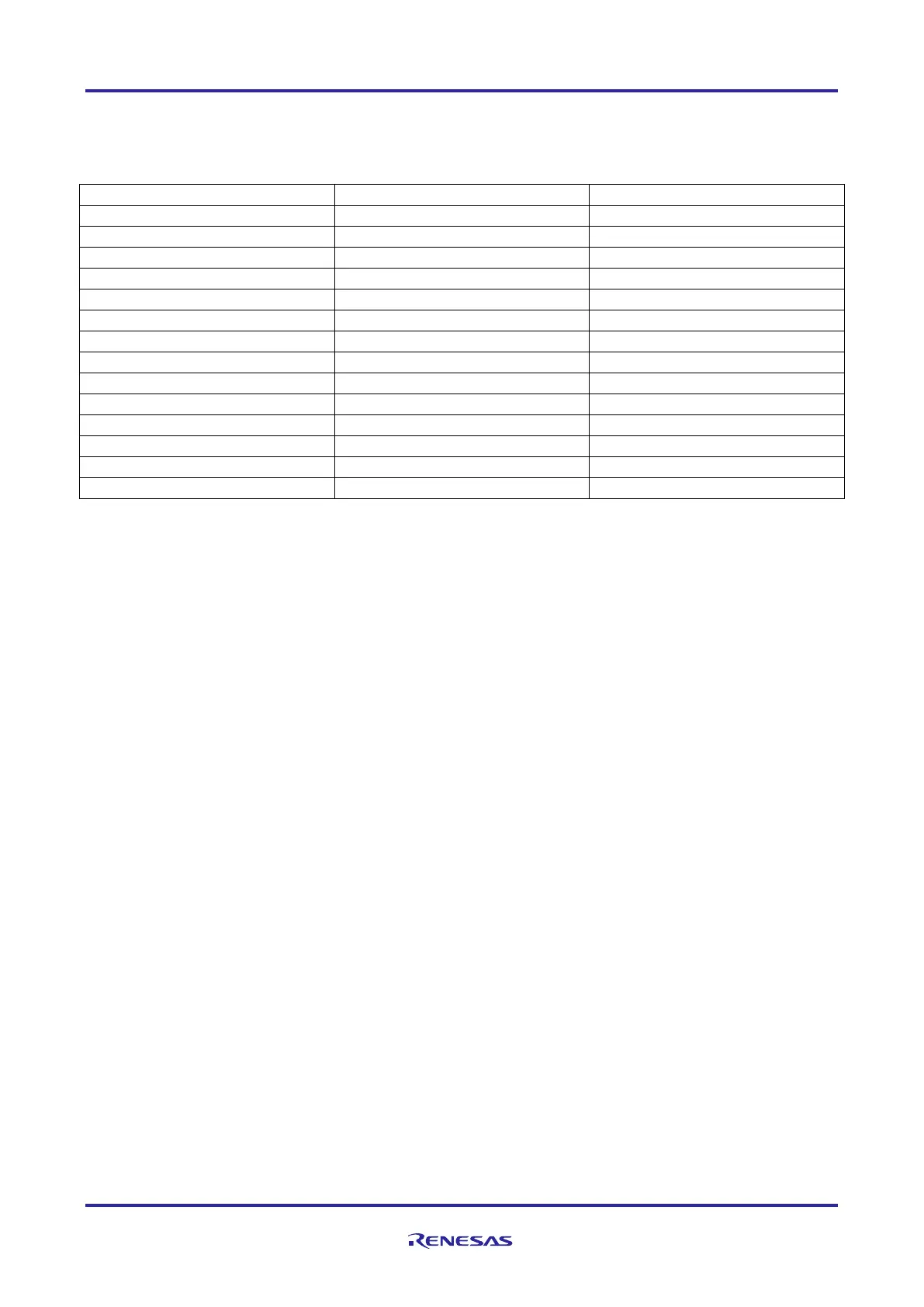

The debug interface signal connection of the E1 interface is given in the table below:

Table 21 Debug interface signal connection of RH850/F1K

Note: The Nexus interface signals marked with (text) are supported by 3rd party development tools and not by E1

emulator.

Caution:

When alternate port functions of P10_8/FLMD1 are used, please make sure not to drive a high level at reset.

When alternate port functions with pull-up resistor are used, please connect P10_8/FLMD1 to FPMD1 of

emulator. In that case, it is kept at a low level by the emulator when the reset signal is released.

Loading...

Loading...