RH850/F1K Series Hardware Design Guide

R01AN2911EJ0100 Rev. 1.00 Page 43 of 46

Aug 04, 2016

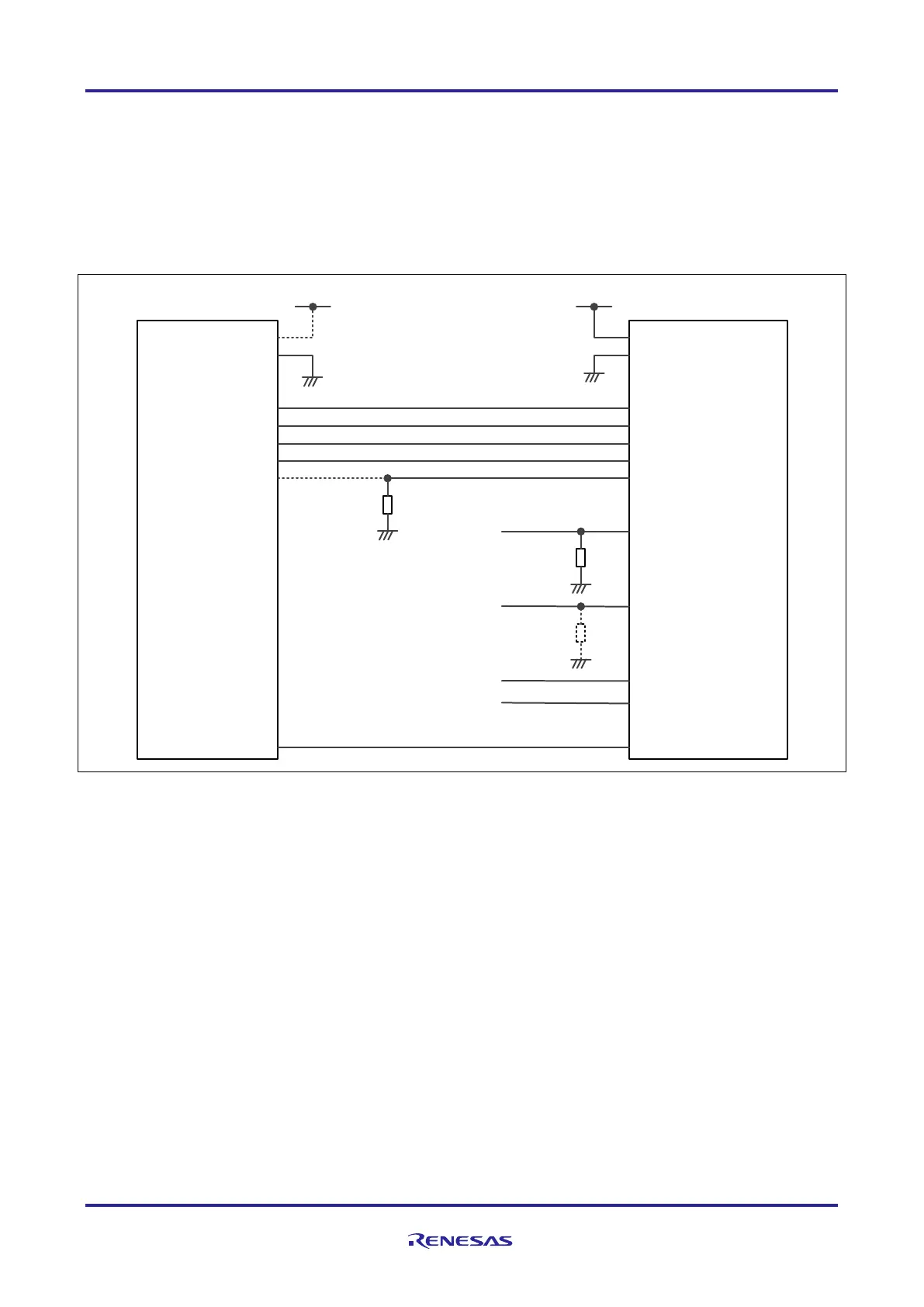

6.2 Boundary Scan Mode Interface of RH850/F1K Group

The boundary scan test is compliant with IEEE Standard 1149.1 and certain boundary scan instructions are supported.

When the boundary scan mode shall be used, several connections have to be done between boundary scan test tool and

the device. Especially the boundary scan mode selection pins have to be considered from application point of view as

these pins are normally used for application related functions.

Figure 23 Boundary scan connection of RH850/F1K

Note: During boundary scan mode the level of the following pins must be fixed: P10_1: Low, P10_2: High, P10_8:

High

In case of the digital I/O pins shared with an analog buffer the boundary scan function only applies to the general I/O

function:

ADCA0: AP0, P8 and P9

ADCA1: AP1, P18

VDD

GND

VDDVDD

EVCC

EVSS

TDI

TDO

TCK

TMS

TRST (optional)

RDY

RESET

RESET

P10_8 (FLMD1)

FLMD0

JP0_0 (DCUTDI)

JP0_1 (DCUTDO)

JP0_2 (DCUTCK)

JP0_3 (DCUTMS)

JP0_4 (DCUTRST)

JP0_5 (DCURDY)

RH850/F1K Group

Boundary Scan Test Tool

(Connector)

100kΩ

1k to 10kΩ

P10_1 (MODE0)

P10_2 (MODE1)

Set to high-level

Set to high-level

Set to low-level

Set to high-level

(optional)

JP0_6 (EVTO)EVTO

10k to 100kΩ

Loading...

Loading...