RH850/F1K Series Hardware Design Guide

R01AN2911EJ0100 Rev. 1.00 Page 7 of 46

Aug 04, 2016

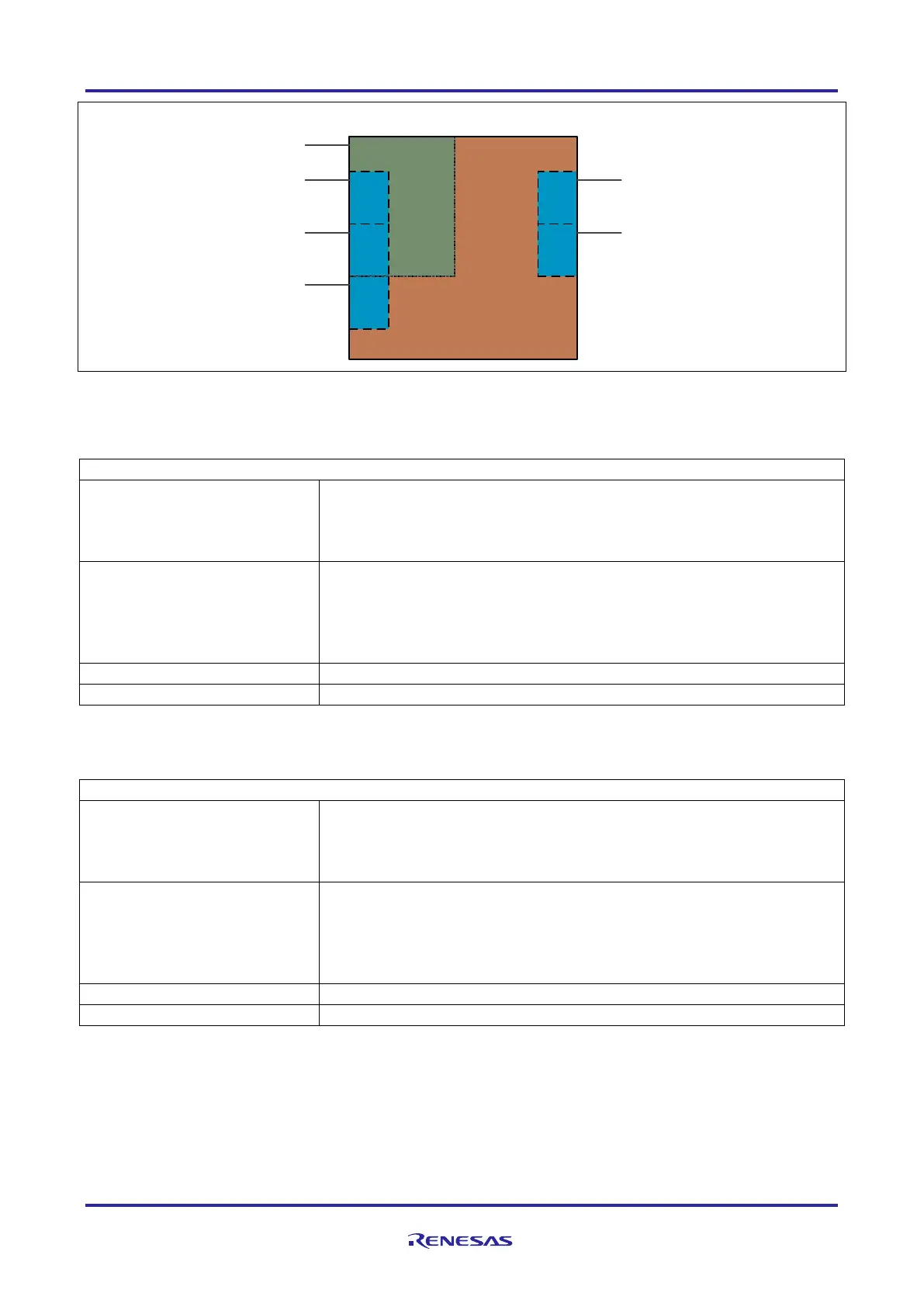

Figure 1 RH850/F1K Power supply architecture

Table 2 Power supply architecture RH850/F1K with single supply 5V

Case 1 – Single Supply 5V

REGVCC = 5V

EVCC = 5V

A0VREF = 5V

A1VREF = 5V

AP0 – Port usable with analog or digital function

P8 – Port usable with analog or digital function

P9 – Port usable with analog or digital function

AP1 – Port usable with analog or digital function

P18 – Port usable with analog or digital function

Table 3 Power supply architecture RH850/F1K with single supply 3.3V

Case 2 – Single Supply 3.3V

REGVCC = 3.3V

EVCC = 3.3V

A0VREF = 3.3V

A1VREF = 3.3V

AP0 – Port usable with analog or digital function

P8 – Port usable with analog or digital function

P9 – Port usable with analog or digital function

AP1 – Port usable with analog or digital function

P18 – Port usable with analog or digital function

RH850/F1K Group

AWO-Area ISO-Area

AP0

P8

P9

AP1

P18

REGVCC

A0VREF

EVCC

EVCC

A1VREF

EVCC

Loading...

Loading...