28

5.1.2 Variable-Size Direct Read/Write

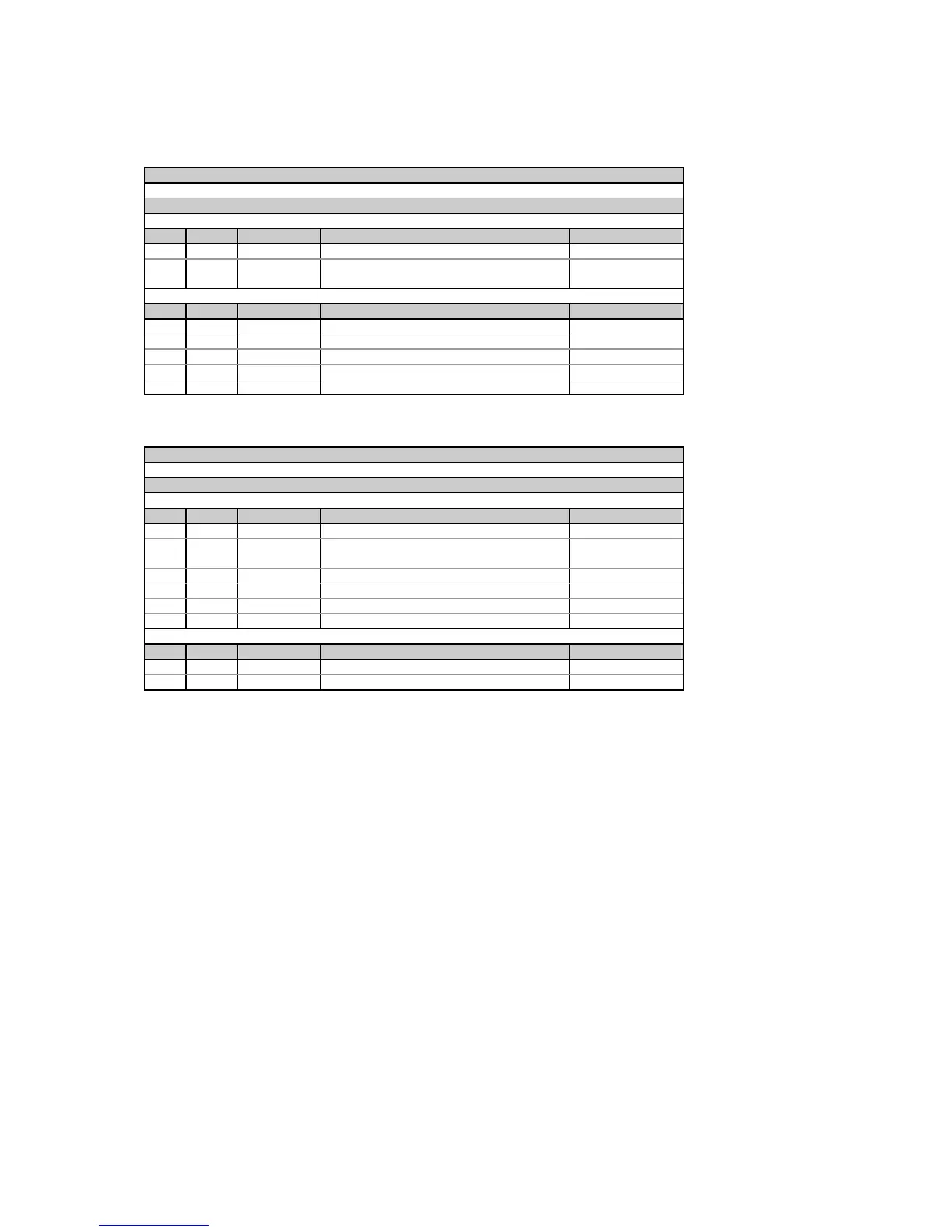

Table 5-3 Read Request

Message type (ASCII)

‘X’

Message body (hexadecimal)

Request

Field Offset Type Parameter Range

1 0 UINT16 Start point (register) ID to read 0x0000 - 0xFFFF

2 4 UINT8 The number of contiguous data items to

read

1-61 (0x01-0x3D)

Response

Field Offset Type Parameter Range

1 0 UINT8 Number of data items in the message 1-61 (0x01-0x3D)

2 2 INT8/16/32 Data #1 value

3 INT8/16/32 Data #2 value

... ... ... ...

60 INT8/16/32 Data #60 value

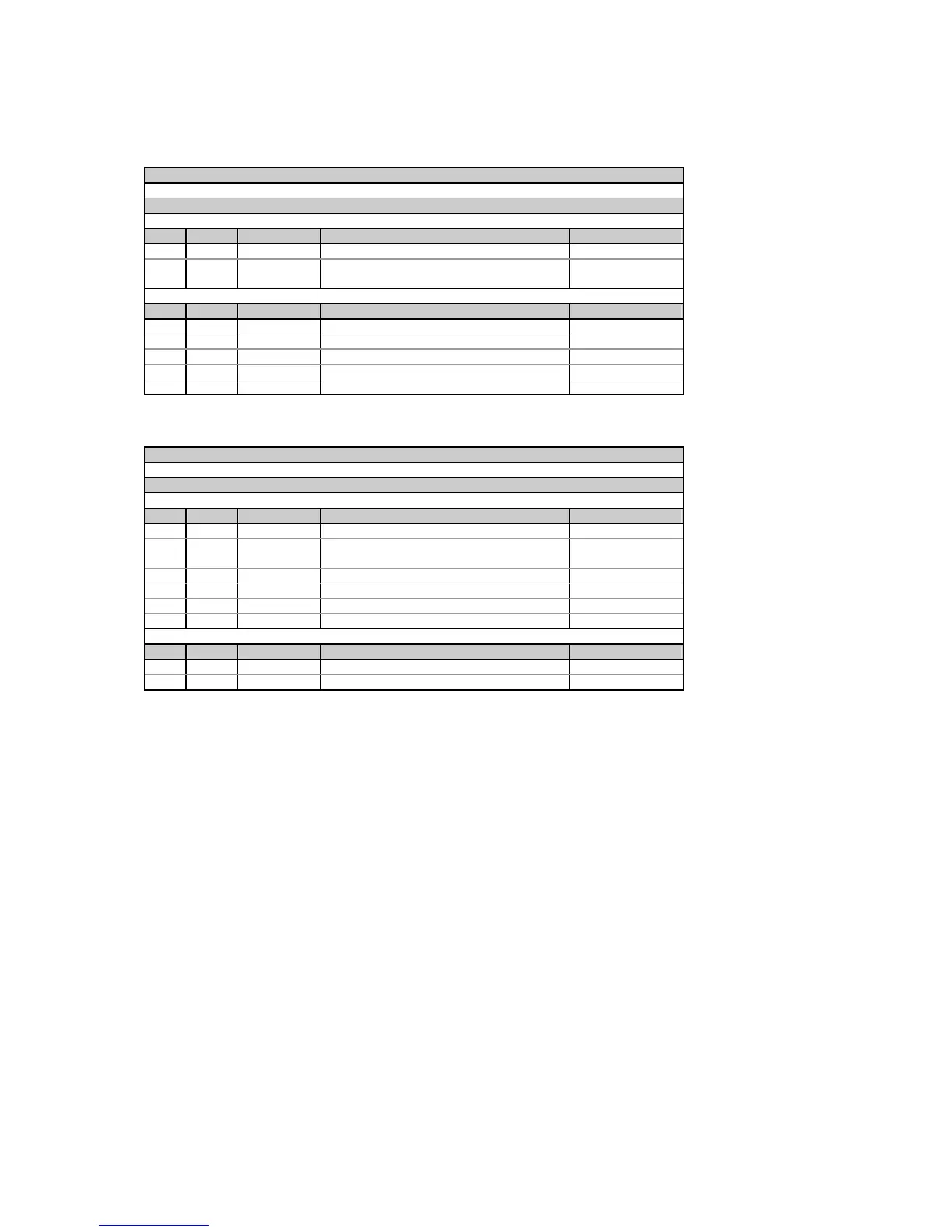

Table 5-4 Write Request

Message type (ASCII)

‘x’

Message body (hexadecimal)

Request

Field Offset Type Parameter Range

1 0 UINT16 Start point (register) ID to write 0x0000 - 0xFFFF

2 4 UINT8 The number of contiguous data items to

write

1-61 (0x01-0x3D)

3 6 INT8/16/32 Data #1 value

4 INT8/16/32 Data #2 value

... ... ... ...

60 INT8/16/32 Data #60 value

Request

Field Offset Type Parameter Range

1 0 UINT16 Start point (register) ID written 0x0000 - 0xFFFF

2 4 UINT8 The number of data items written 1-61 (0x01-0x3D)

With variable-size direct read/write messages, data items are read and written as 2, 4 or 8-character hexadecimal

numbers. The actual data size is indicated for each data location. When written, the data format should be exactly

the same as indicated.

The number of parameters that can be read or written by a single read/write request depends on the size of each

data item. The total length of all parameters should not exceed 240 characters.

5.1.3 User Assignable Registers

The instrument contains 120 user assignable registers in the range of addresses 0x8000 to 0x8077 (see Table

5-5). You can map any of these registers to either register address, accessible in the instrument through direct

read/write requests. Registers that reside in different locations may be accessed by a single request by re-

mapping them to adjacent addresses in the user assignable registers area.

The actual addresses of the user assignable registers, which are accessed via points 0x8000 to 0x8077, are

specified in the user assignable register map. It occupies addresses 0x8100 to 0x8177 (see Table 5-6), where the

map register 0x8100 should contain the actual address of the register accessed via assignable register 0x8000,

register 0x8101 should contain the actual address of the register accessed via assignable register 0x8001, and so

on. Note that the user assignable registers and the user register map addresses may not be re-mapped.

Loading...

Loading...