06.03

7.3 SIMATIC S7 project

7-229

Siemens AG, 2003. All rights reserved

SINUMERIK 840Di Manual (HBI) – 06.03 Edition

Once the components (drives, ADI4, I/O devices, etc.) have been inserted in the

configuration and parameterized, the parameters are set for the equidistant DP

cycle while taking the framework conditions listed below into consideration, (see

Subsection 7.3.8, page 7-238).

When setting the parameters for the equidistant DP cycle, with ADI4 it is neces-

sary to take the following framework conditions into account:

Factor

General

Equidistant bus cycle activated

Network settings in msec:

Synchronize drive to equidistant DP cycle

Clock synchronizationConfiguration

Cyclic portion of equidistant master

Setpoint acceptance

[msec]:

Actual-value sensing

[msec]:

Basic time [msec]

Master application cycle

[msec]:

2.000

Equidistant DP cycle:

0.872

DP cycle [msec]:

2.000

2.000 2.000

0.125

0.125

0.1258

2

16

1

1.000

0.250

DP slave properties

Factor

Factor

Factor

Basic time [msec]

Basic time [msec]

Basic time [msec]

=

=

=

=

x

x

x

x

T

I

TDXT

DP

T

O

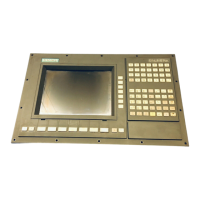

Fig. 7-6 Dialog: DP slave properties (cutout)

1. Equidistant DP cycle (T

DP

)

T

DP

= 2* n * 125msec; where n w 4 ( => minimum T

DP

= 1 msec)

2. Setpoint acceptance (T

o

)

(TDX + 125msec) v T

O

t T

DP

; where TDX = T

DX

, rounded up to an

integral multiple of 125msec

3. Actual-value sensing (T

i

)

250msec v T

I

v T

DP

4. T

I

and T

O

must not be in the same 125msec cycle

DT , 0; where DT = T

DP

–

T

I

–

T

O

5. If T

O

== (T

DP

– 125msec)

Then the following must be valid for T

I

: T

I

u 3 * 125msec

6. If T

O

== (TDX + 125msec)

Then the following must be valid for (T

I

+ T

O

): (T

I

+ T

O

) , (T

DP

+ 125msec)

T

DP

1*125msec

T

I

2*125msec 3*125msec 4*125msec 5*125msec 6*125msec 7*125msec 8*125msec

T

O

ÉÉÉÉÉÉÉÉÉÉÉÉÉÉ

ÉÉÉÉÉÉÉÉÉÉÉÉÉÉ

Min.: 2*125msec

Max.: T

DP

DT 0

Min.: TDX+125msec

T

DX

Max.: T

DP

Fig. 7-7 Graphical illustration of the boundary conditions

Setting the final

parameters for

ADI4

Boundary

conditions

(SW 2.1 and

higher)

7 PROFIBUS DP Communication